$\rm N^o$ d'ordre : XXXX

## THÈSE

PRÉSENTÉE À

## L'UNIVERSITÉ DE BORDEAUX

ÉCOLE DOCTORALE DE MATHÉMATIQUES ET D'INFORMATIQUE

Par Xavier LACOSTE

POUR OBTENIR LE GRADE DE

DOCTEUR

SPÉCIALITÉ : INFORMATIQUE

Scheduling and memory optimizations for sparse direct solver on multi-core/multi-gpu cluster systems

### Soutenue le : 18 Février 2015

#### Après avis des rapporteurs :

| Timothy A. DAVIS | Professor, Texas A&M University     |

|------------------|-------------------------------------|

| Xiaoye Sherry LI | Senior Scientist, Lawrence Berkeley |

|                  | National Laboratory                 |

#### Devant la commission d'examen composée de :

| Alfredo Buttari<br>Fredéric Desprez | Researcher, CNRS IRIT, Toulouse<br>Senior researcher, INRIA, Grenoble | Membre du Jury<br>Membre du Jury |

|-------------------------------------|-----------------------------------------------------------------------|----------------------------------|

| Iain S. DUFF                        | Professor, Rutherford Appleton                                        | Membre du Jury                   |

|                                     | Laboratory, Oxfordshire                                               |                                  |

| Guillaume LATU                      | Research scientist, CEA Cadarache                                     | Membre du Jury                   |

| Boniface NKONGA                     | Professor, Université de Nice,                                        | Membre du Jury                   |

| François Pellegrini                 | Professor, Université de Bordeaux                                     | Directeur de Thèse               |

| Pierre RAMET                        | Assistant professor, Université de Bordeaux                           | Directeur de Thèse               |

|                                     |                                                                       |                                  |

Acknowledgements

### Ordonnancement et optimisations mémoire pour un solveur creux par méthodes directes sur des machines hétérogènes

Résumé : L'évolution courante des machines montre une croissance importante dans le nombre et l'hétérogénéité des unités de calcul. Les développeurs doivent alors trouver des alternatives aux modèles de programmation habituels permettant de produire des codes de calcul à la fois performants et portables. PASTIX est un solveur parallèle de système linéaire creux par méthodes directe. Il utilise un ordonnanceur de tâche dynamique pour être efficaces sur les machines modernes multi-cœurs à mémoires hiérarchiques. Dans cette thèse, nous étudions les bénéfices et les limites que peut nous apporter le remplacement de l'ordonnanceur interne, très spécialisé, du solveur PASTIX par deux systèmes d'exécution génériques : PARSEC et STARPU. Pour cela l'algorithme doit être décrit sous la forme d'un graphe de tâches qui est fournit aux systèmes d'exécution qui peuvent alors calculer une exécution optimisée de celui-ci pour maximiser l'efficacité de l'algorithme sur la machine de calcul visée. Une étude comparative des performances de PASTIX utilisant ordonnanceur interne, PARSEC, et STARPU a été menée sur différentes machines et est présentée ici. L'analyse met en évidence les performances comparables des versions utilisant les systèmes d'exécution par rapport à l'ordonnanceur embarqué optimisé pour PASTIX. De plus ces implémentations permettent d'obtenir une accélération notable sur les machines hétérogènes en utilisant les accélérateurs tout en masquant la complexité de leur utilisation au développeur. Dans cette thèse nous étudions également la possibilité d'obtenir un solveur distribué de système linéaire creux par méthodes directes efficace sur les machines parallèles hétérogènes en utilisant les systèmes d'exécution à base de tâche. Afin de pouvoir utiliser ces travaux de manière efficace dans des codes parallèles de simulations, nous présentons également une interface distribuée, orientée éléments finis, permettant d'obtenir un assemblage optimisé de la matrice distribuée tout en masquant la complexité liée à la distribution des données à l'utilisateur.

**Mots clés :** Résolution de systèmes linéaires creux, ordonnanceur à base de tâches, MPI, multi-cœur, GPU.

**Discipline :** Informatique

LABRI (UMR CNRS 5800) Université de Bordeaux, 351, cours de la libération 33405 Talence Cedex, FRANCE Equipe Projet INRIAHiePACS<sup>1</sup>, INRIA Bordeaux – Sud-Ouest, 200, avenue de la vieille tour, 33405 Talence Cedex, FRANCE

<sup>&</sup>lt;sup>1</sup>HiePACS: High-End Parallel Algorithms for Challenging Numerical Simulations, https://team. inria.fr/hiepacs/.

# Scheduling and memory optimizations for sparse direct solver on multi-core/multi-gpu cluster systems

**Abstract:** The ongoing hardware evolution exhibits an escalation in the number, as well as in the heterogeneity, of computing resources. The pressure to maintain reasonable levels of performance and portability forces application developers to leave the traditional programming paradigms and explore alternative solutions. PASTIX is a parallel sparse direct solver, based on a dynamic scheduler for modern hierarchical manycore architectures. In this thesis, we study the benefits and the limits of replacing the highly specialized internal scheduler of the PASTIX solver by two generic runtime systems: PARSEC and STARPU. Thus, we have to describe the factorization algorithm as a tasks graph that we provide to the runtime system. Then it can decide how to process and optimize the graph traversal in order to maximize the algorithm efficiency for the targeted hardware platform. A comparative study of the performance of the PASTIX solver on top of its original internal scheduler, PARSEC, and STARPU frameworks is performed. The analysis highlights that these generic task-based runtimes achieve comparable results to the application-optimized embedded scheduler on homogeneous platforms. Furthermore, they are able to significantly speed up the solver on heterogeneous environments by taking advantage of the accelerators while hiding the complexity of their efficient manipulation from the programmer. In this thesis, we also study the possibilities to build a distributed sparse linear solver on top of task-based runtime systems to target heterogeneous clusters. To permit an efficient and easy usage of these developments in parallel simulations, we also present an optimized distributed interface aiming at hiding the complexity of the construction of a distributed matrix to the user.

**Keywords:** Sparse direct solver, Tasks based runtime systems, MPI, multi-core, GPU.

**Discipline :** Computer science

LABRI (UMR CNRS 5800) Université Bordeaux 1, 351, cours de la libération 33405 Talence Cedex, FRANCE Equipe Projet INRIA HiePACS<sup>2</sup>, INRIA Bordeaux – Sud-Ouest, 200, avenue de la vieille tour, 33405 Talence Cedex, FRANCE

<sup>2</sup>HiePACS: High-End Parallel Algorithms for Challenging Numerical Simulations, https://team. inria.fr/hiepacs/. vi

# Contents

| In | trod | uction  |                                                    | 1  |

|----|------|---------|----------------------------------------------------|----|

| 1  | Line | ear alg | ebra on modern architectures                       | 5  |

|    | 1.1  | Paralle | el architectures                                   | 6  |

|    |      | 1.1.1   | Multi-core machines                                | 6  |

|    |      | 1.1.2   | Accelerators                                       | 8  |

|    | 1.2  | Addres  | ssing parallel machines                            | 10 |

|    |      | 1.2.1   | Parallel programming                               | 11 |

|    |      | 1.2.2   | Addressing accelerators                            | 14 |

|    |      | 1.2.3   | Task-based runtime systems                         | 14 |

|    | 1.3  | Sparse  | linear algebra methods                             | 16 |

|    |      | 1.3.1   | Prerequisite: Basic Linear Algebra Subroutines     | 17 |

|    |      | 1.3.2   | Solving a sparse linear system                     | 18 |

|    |      | 1.3.3   | Description of the direct methods                  | 20 |

|    |      | 1.3.4   | Linear algebra on homogeneous clusters             | 29 |

|    |      | 1.3.5   | Linear algebra on heterogeneous clusters           | 31 |

|    | 1.4  | Discus  | sion                                               | 35 |

| 2  | Spa  | rse fac | torization on shared-memory heterogeneous machines | 37 |

|    | 2.1  | Frame   | work                                               | 39 |

|    |      | 2.1.1   | PASTIX original algorithm description              | 39 |

|    |      | 2.1.2   | Elected runtime systems                            | 41 |

|    | 2.2  | Impler  | nentation on top of generic runtime systems        | 49 |

|    |      | 2.2.1   | PARSEC implementation                              | 50 |

|    |      | 2.2.2   | STARPU implementation                              | 53 |

|    |      | 2.2.3   | Multi-core Architecture experimentation            | 55 |

|   | 2.3  | Heterog  | geneous systems                                                                                                 | 57  |

|---|------|----------|-----------------------------------------------------------------------------------------------------------------|-----|

|   |      | 2.3.1    | Implementation of a specific GEMM kernel                                                                        | 60  |

|   |      | 2.3.2    | Data mapping over multiple GPUs                                                                                 | 66  |

|   |      | 2.3.3    | Heterogeneous experiments                                                                                       | 69  |

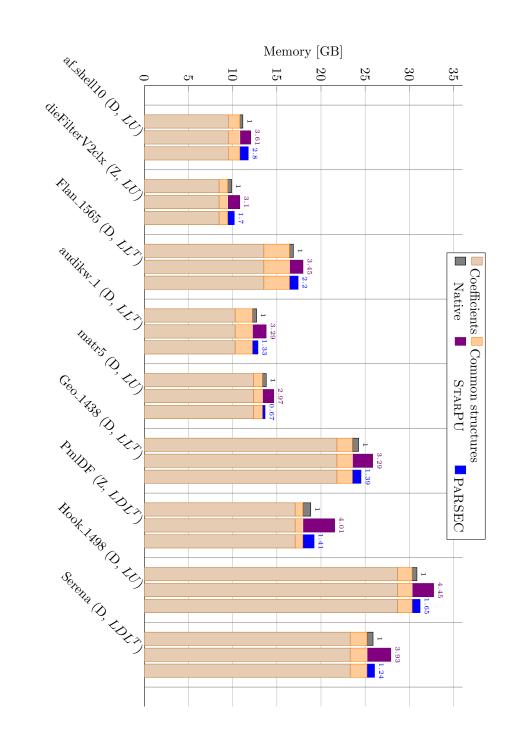

|   |      | 2.3.4    | Memory study                                                                                                    | 69  |

|   | 2.4  | Optimi   | izations                                                                                                        | 71  |

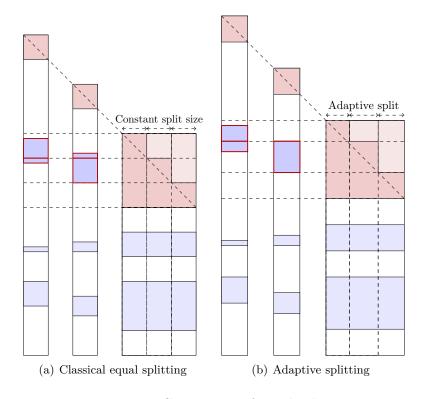

|   |      | 2.4.1    | Task granularity adapted to the runtime                                                                         | 71  |

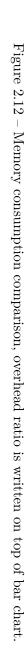

|   |      | 2.4.2    | Block splitting algorithm                                                                                       | 73  |

|   | 2.5  | Discuss  | sion                                                                                                            | 79  |

| 3 | Spa  | rse fact | torization on distributed heterogeneous systems                                                                 | 83  |

|   | 3.1  | Solving  | g distributed sparse linear system                                                                              | 84  |

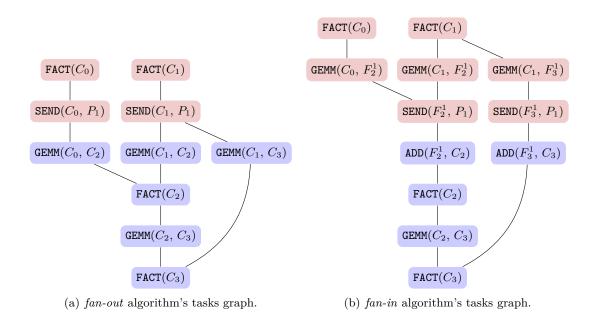

|   |      | 3.1.1    | Fan-out implementation                                                                                          | 84  |

|   |      | 3.1.2    | Fan-in implementation                                                                                           | 86  |

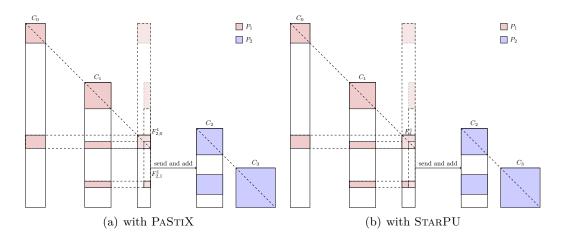

|   |      | 3.1.3    | Data mapping                                                                                                    | 89  |

|   | 3.2  | Experi   | ments                                                                                                           | 92  |

|   |      | 3.2.1    | Distributed implementation on homogeneous nodes                                                                 | 92  |

|   |      | 3.2.2    | Distributed implementation on heterogeneous nodes $\ldots \ldots \ldots$                                        | 97  |

|   | 3.3  | Discuss  | sion                                                                                                            | 99  |

| 4 | Inte | 0        | •                                                                                                               | 03  |

|   | 4.1  | Descrip  | ption of the framework                                                                                          | .04 |

|   |      | 4.1.1    | Set of equations                                                                                                | .05 |

|   |      | 4.1.2    | Spatial discretization                                                                                          | 05  |

|   |      | 4.1.3    | Time integration scheme                                                                                         | .06 |

|   |      | 4.1.4    | Equilibrium                                                                                                     | .06 |

|   |      | 4.1.5    | Sparse solver and preconditioning                                                                               | .07 |

|   | 4.2  | Assemb   | bly step in JOREK                                                                                               | .08 |

|   | 4.3  | Optimi   | ized distributed matrix assembly                                                                                | 12  |

|   |      | 4.3.1    | Generic distributed finite element assembly oriented API $\ . \ . \ . \ .$                                      | 13  |

|   |      | 4.3.2    | $Comparison \ with \ PETSc \ \ \ldots $ | 15  |

|   | 4.4  | Integra  | tion into JOREK                                                                                                 | .18 |

|   |      | 4.4.1    | Implementation                                                                                                  | 18  |

|   |      | 4.4.2    | Timing and memory scaling study                                                                                 | 19  |

|              |       |                                    | ix  |

|--------------|-------|------------------------------------|-----|

|              | 4.5   | Discussion                         | 121 |

| Co           | onclu | sion and perspectives              | 123 |

| Aj           | ppen  | dixs                               | 127 |

| $\mathbf{A}$ | Pub   | lications                          | 127 |

| в            | Inte  | gration in Algo'Tech software      | 129 |

|              | B.1   | Algo'Tech software simulation tool | 129 |

|              | B.2   | Optimizations                      | 130 |

|              |       | B.2.1 PASTIX integration           | 130 |

|              |       | B.2.2 Parallelization              | 130 |

|              |       | B.2.3 Cloud computing              | 130 |

|              |       | B.2.4 Numerical optimization       | 131 |

|              | B.3   | Conclusion                         | 131 |

| С            | Mu    | ge and Jorek code samples          | 133 |

| D            | Spa   | rse matrix storage formats         | 139 |

# List of Figures

| 1.1  | A four CPUs SMP machine                                                 | 7              |

|------|-------------------------------------------------------------------------|----------------|

| 1.2  | A four CPUs NUMA machine                                                | $\overline{7}$ |

| 1.3  | Architecture of the NVIDIA Kepler GK110.                                | 9              |

| 1.4  | Architecture of the Intel Xeon Phi.                                     | 11             |

| 1.5  | A Mirage node described using Hardware Locality (hwloc) tool            | 12             |

| 1.6  | Reordering of the unknowns.                                             | 22             |

| 1.7  | A block structure factorized matrix and the associated elimination tree | 23             |

| 1.8  | Description of the notations used for the factorization algorithm       | 24             |

| 1.9  | Multifrontal algorithm                                                  | 25             |

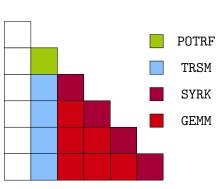

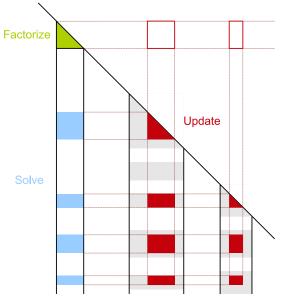

| 2.1  | Notations used in algorithms                                            | 42             |

| 2.2  | Comparison of dense and sparse task decomposition                       | 51             |

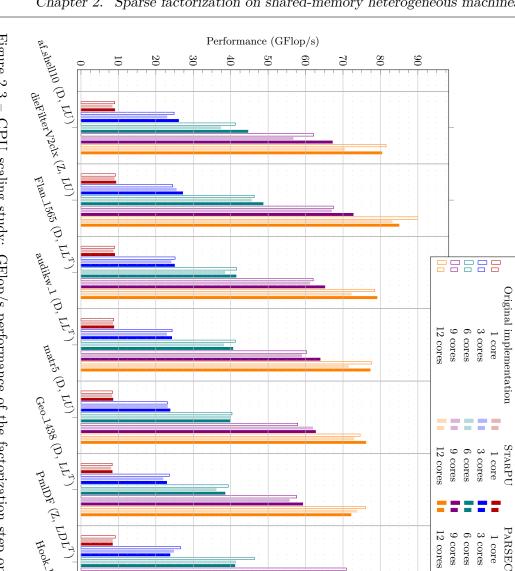

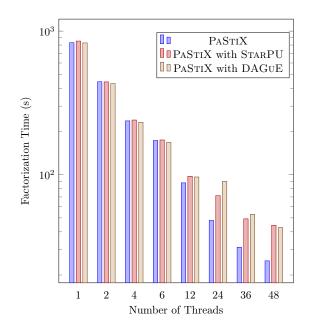

| 2.3  | CPU scaling study on 12 cores                                           | 58             |

| 2.4  | CPU scaling study on 48 cores                                           | 59             |

| 2.5  | Description of the panel update task                                    | 61             |

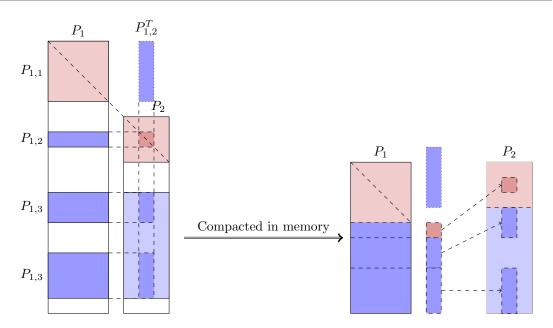

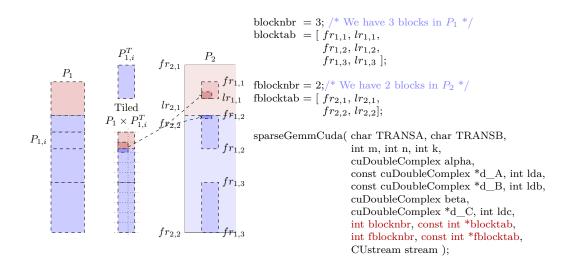

| 2.6  | Description of the GPU sparse GEMM update operation                     | 62             |

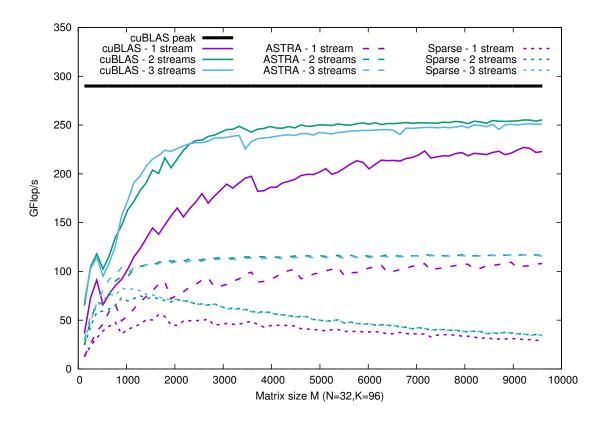

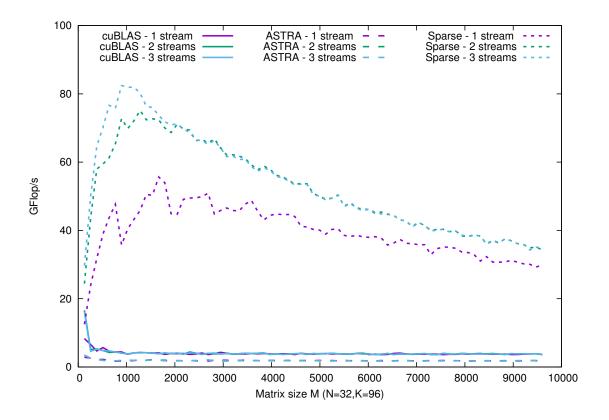

| 2.7  | Performance study on the DGEMM kernel (sparse vs dense)                 | 63             |

| 2.8  | Performance study on the DGEMM kernel (sparse vs multiple CUDA calls).  | 65             |

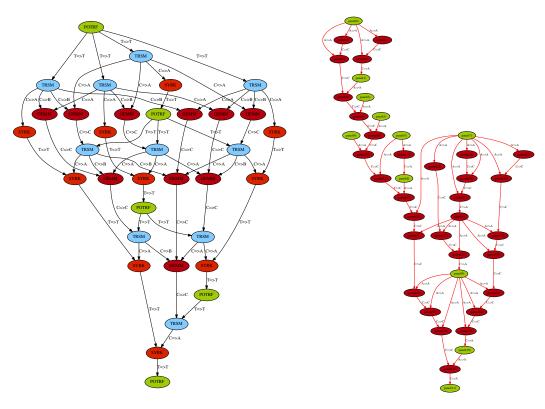

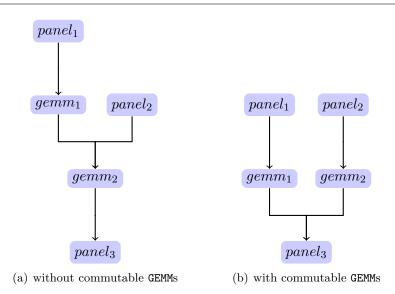

| 2.9  | Effects of commutable tasks on the graph                                | 66             |

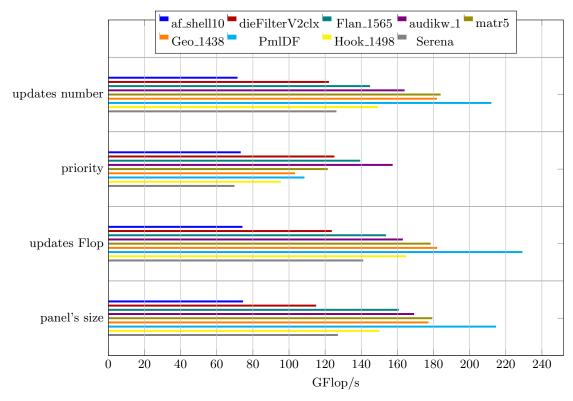

| 2.10 | Sort criteria study.                                                    | 68             |

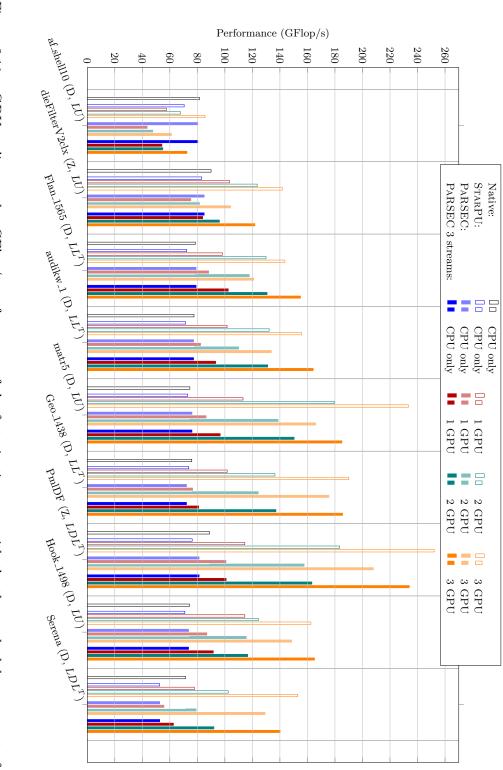

| 2.11 | GPU scaling study                                                       | 70             |

| 2.12 | Memory consumption comparison.                                          | 72             |

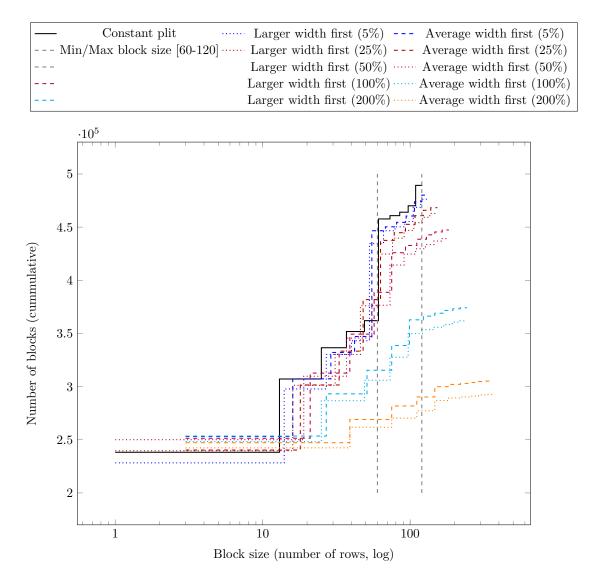

| 2.13 | Comparison of panel splitting                                           | 74             |

| 2.14 | Flop/s during factorization depending on authorized variation in column |                |

|      | block splits                                                            | 77             |

| 2.15 | Block's size study.                                                     | 78             |

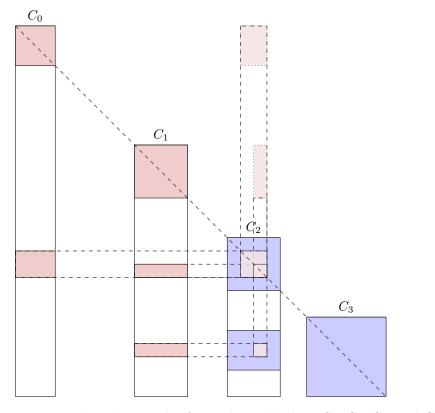

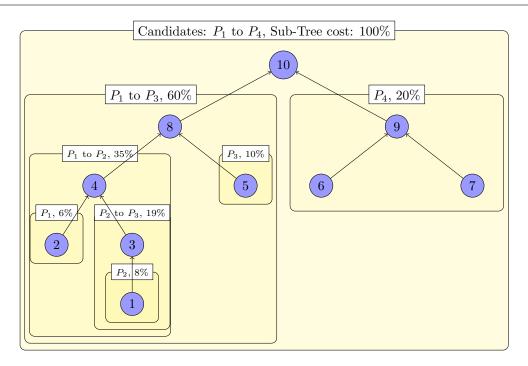

| 3.1  | Distributed example.                                                    | 85             |

| 3.2  | Distributed algorithm's task graph                                      | 88             |

| 3.3  | Fan-In distributed example.                                             | 90             |

| 3.4  | Proportional mapping                                                    | 91             |

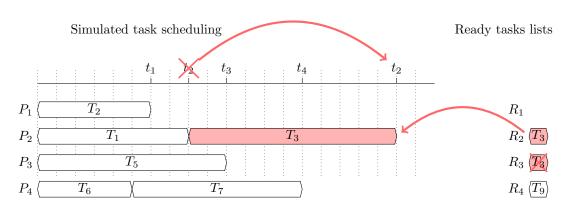

| 3.5  | Simulated static scheduling                                             | 92             |

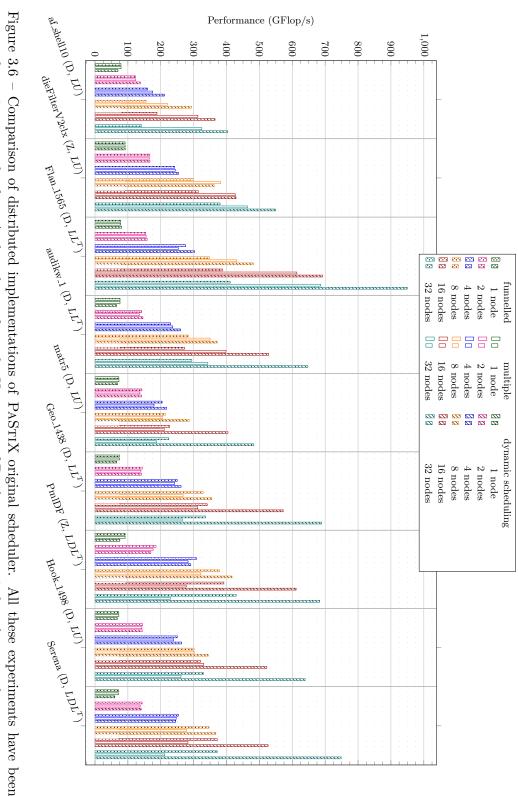

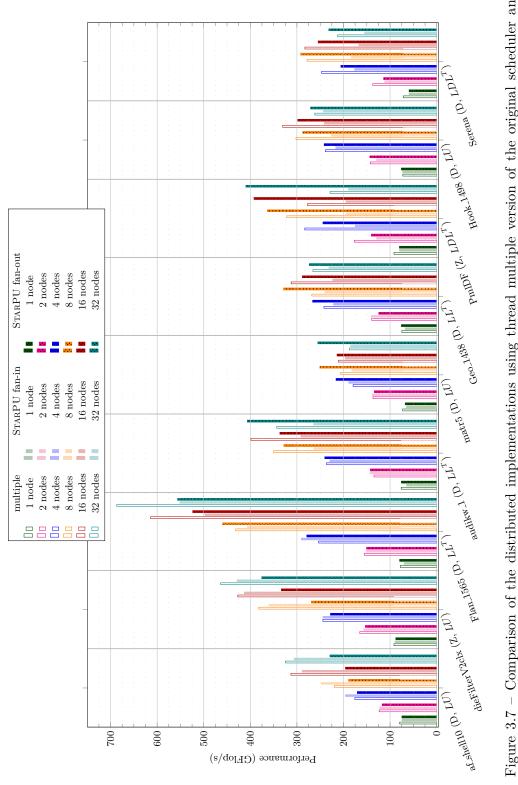

| 3.6  | Comparison of distributed implementations of PASTIX original scheduler. | 94             |

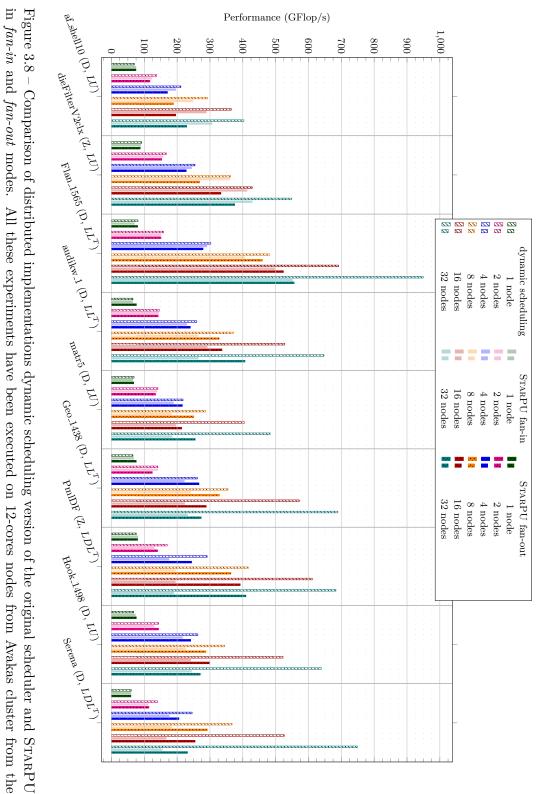

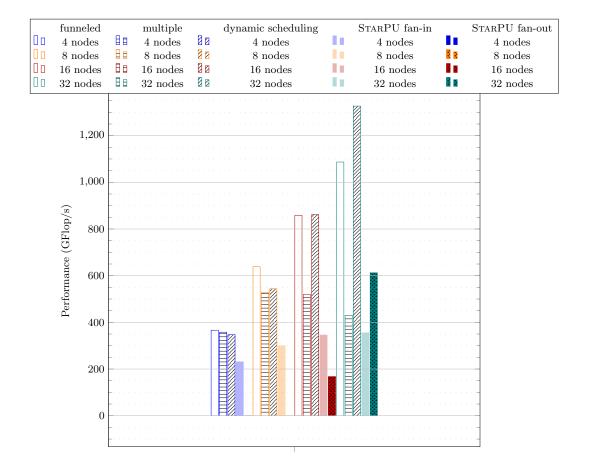

| 3.7  | Comparison of distributed implementations: original scheduler vs $STARPU$ . 95 |

|------|--------------------------------------------------------------------------------|

| 3.8  | Comparison of distributed implementations: dynamic scheduling vs               |

|      | StarPU                                                                         |

| 3.9  | Comparison of distributed implementations on the 10 Millions test case $98$    |

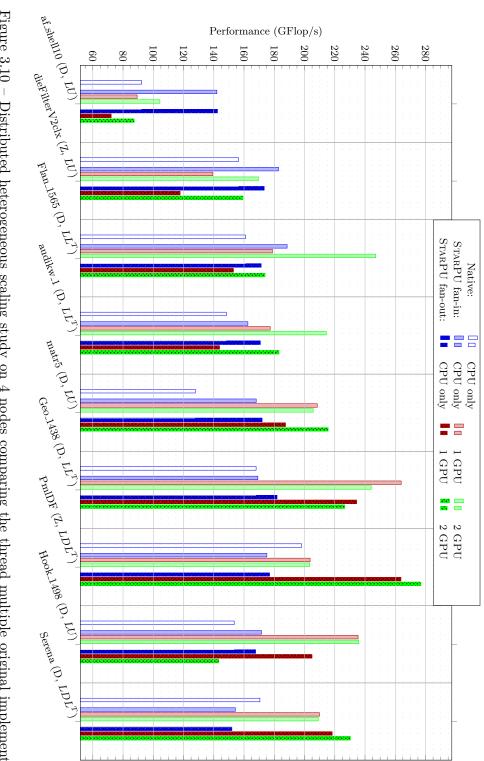

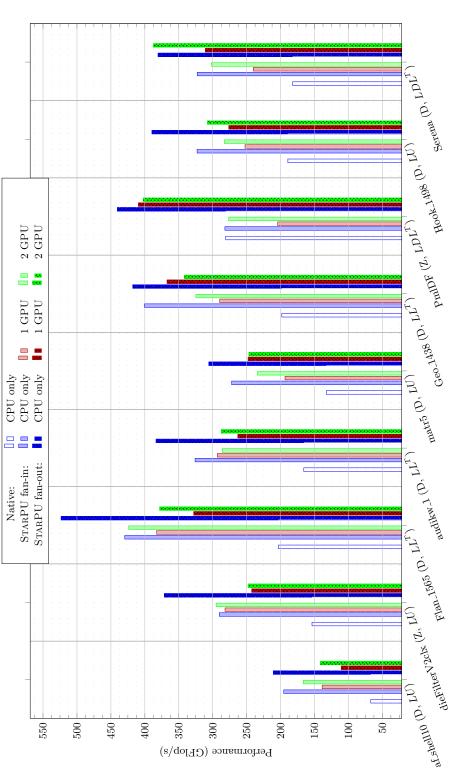

| 3.10 | Distributed heterogeneous scaling study on 4 nodes                             |

| 3.11 | Distributed heterogeneous scaling study on 16 nodes                            |

|      |                                                                                |

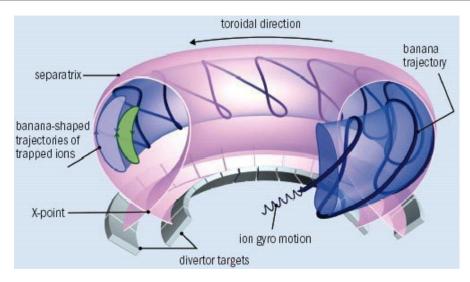

| 4.1  | A tokamak                                                                      |

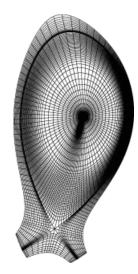

| 4.2  | Bezier 2D representation of a tokamak's plan                                   |

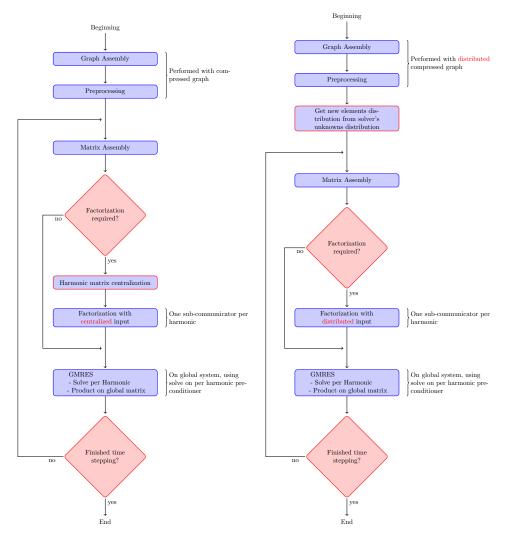

| 4.3  | JOREK main steps diagram                                                       |

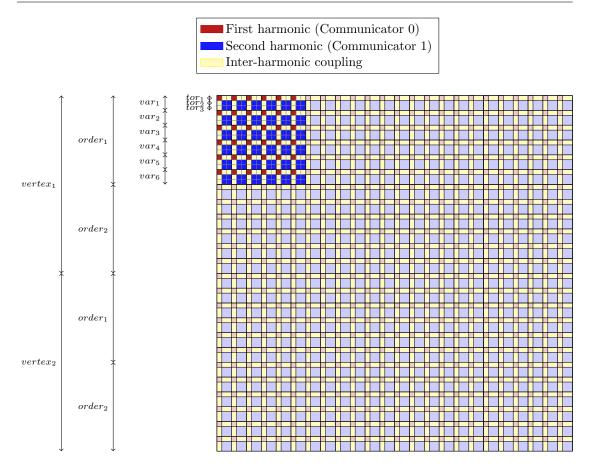

| 4.4  | Part of JOREK's elementary matrix                                              |

| 4.5  | JOREK's assembled matrix                                                       |

| 4.6  | Different assembly methods                                                     |

| 4.7  | Timing scaling study comparing PETSc and MURGE assembly 117                    |

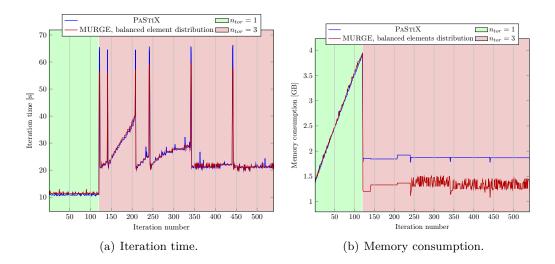

| 4.8  | Time and memory comparison on model 302 (2 harmonics)                          |

| 4.9  | Time and memory comparison on model 303 (2 harmonics)                          |

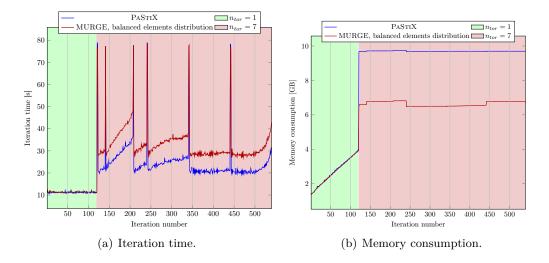

| 4.10 | Time and memory comparison on model 303 (4 harmonics)                          |

|      |                                                                                |

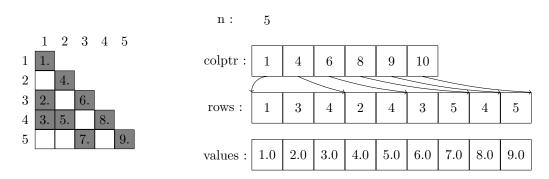

| D.1  | An example of CSC matrix                                                       |

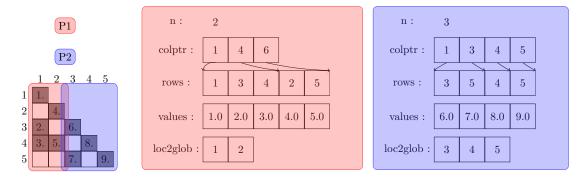

| D.2  | An example of CSCD matrix                                                      |

# List of Tables

| 2.1 | Descriptions of the matrices.                   | 56 |

|-----|-------------------------------------------------|----|

| 2.2 | Comparison of the different splitting methods   | 76 |

| 3.1 | Comparison of the <i>fan-in</i> memory overhead | 90 |

# List of Algorithms

| 1  | Multi-frontal factorization: $A = LU$                            |

|----|------------------------------------------------------------------|

| 2  | Right looking blocked sequential factorization: $A = LU$         |

| 3  | Left looking blocked sequential factorization: $A = LU$          |

| 4  | Parallel column-block factorization on thread $t$ of process $p$ |

| 5  | STARPU tasks insertion algorithm                                 |

| 6  | Adapted splitting algorithm                                      |

| 7  | Choice of the split: largest first                               |

| 8  | Choice of the split: average first                               |

| 9  | Fan-out Cholesky implementation with STARPU                      |

| 10 | Fan-in Cholesky implementation with STARPU                       |

| 11 | Frequencies loop using a classical direct solver                 |

| 12 | Frequencies loop with direct preconditionned iterative solver    |

| 13 | Assembly algorithm using original PASTIX interface               |

| 14 | Assembly algorithm using MURGE API $(1/2)$                       |

| 15 | Assembly algorithm using MURGE API $(2/2)$                       |

|    |                                                                  |

# Introduction

Scientists have always wanted to acquire more accurate knowledge of their surroundings. They realized experiments to explain and predict the universe. With the computers emergence, a new discipline that greatly accelerated this process appeared: computational science. Indeed, computers are capable of simulating experiments that can validate new concepts or designs with an accuracy never seen before. Indeed, using numerical simulations one can avoid setting up expensive, complicated, time-consuming, or dangerous experiments. Moreover, simulations can be used in various fields such as: aerodynamic field, oil prospecting, meteorology, biology, finance, etc. This list is not exhaustive but shows how simulations can affect many fields on a day to day basis environment. Thus, numerical simulation is a very active research field: simulations must be both accurate and fast. Particularly, nuclear fusion reactors are a promising research field for our future as a new source of energy, and require very accurate simulations. A good example is the nuclear fusion reactor prototype ITER (International Thermonuclear Experimental Reactor) built in Cadarache, France and for which a simulation code, JOREK, has been developed to design and calibrate its pieces.

Generally, the studied problem cannot be solved continuously on the whole domain, but it has to be studied in many points. The separation of the domain into many pieces is called the discretization. The discrete equations are a restriction of the mathematical continuous equations on the domain discretization. These discrete equations form a system of equations that can also be viewed as a matrix where the entries are the coefficients of the system. This system can be either dense, if we consider each point of the discretization has an influence to all other points. Then, a corresponding matrix that stores those influences contains nearly no nil values and is called *dense*. In some cases, some of the interactions can be neglected, which translates to nil entries in the matrix. When the number non zeros entries is of the same order of magnitude as its number of equations, the matrix is said to be *sparse*. As the accuracy of the expected solution and the size of the problem increase, the number of unknowns in the system gets larger, reaching several tens of millions unknowns in many simulations. For example, to capture all the phenomena in the atmosphere, a meteorologic simulation must be very sharp, with the smallest distance between discretization points as possible. However, one would want to obtain the solution as fast as possible (e.g. a weather forecast should be computed before it happened), but the time required to solve the system increases (linear to cubic increase depending on the method) with the number of unknowns. Either we reduce the accuracy of the solution by spreading the discretization points, or we accelerate the numerical simulation to obtain the solution in a bounded time. Thus, scientists developed parallel techniques to benefit from multiple computers within one simulation. Furthermore, different methods have been developed to solve the linear systems induced by those simulations, varying in term of complexity and accuracy. Thanks to these techniques and increasingly more efficient chips, scientists can increase the domain size and use a more accurate representation to solve problems with a larger number of unknowns in the same computational time.

Nowadays, machine manufacturers have reached a limit in the performance of a single computational core. Indeed, the clock frequency of chips has not improved significantly since 2004 because of the heat dissipation increase [sutter free 2005]. In the last decade, machines computational power has been increased using multi-core chips able to compute a larger number of operations per cycle. High performance computing clusters are now based of about nodes with 16 to 64 cores interconnected with high performance networks. These machines feature a hierarchical access to the memory and are called NUMA<sup>3</sup> nodes. The current trend in high performance computing is to assist the traditional cores with accelerators to speed-up certain categories of operation. This idea of using an accelerator is not new in high performance computing, but the new usage of Graphic Processing Units for computations brought to manufacturers affordable accelerators. These accelerators are massively parallel and require very regular computations on a vector of data (they are SPMD<sup>4</sup> computational units). Intel has also produced a many-core accelerator, the Intel Xeon Phi, which also requires the programmer to extract a lot of parallelism from its algorithms. All these different chips require specific programming optimizations to be used efficiently. To address these complex heterogeneous machines, new parallel programming models have been designed. Among them, the task-based runtime systems propose to isolate the algorithm from the architecture management. Task-based runtime systems are middle-wares that have been designed to estimate concurrency between tasks and execute them in parallel using all the computational devices of a machine. These runtime systems are also capable of moving data between the devices to relieve the application developer from taking care of data coherency. Using these systems, the developer can obtain more adaptability of the code, and the performance portability is more easily reachable thanks to the separation of the algorithm from the hardware management.

The dense linear algebra community has led multiple studies on heterogeneous computing, often using task-based runtime systems [planas\_hierarchical\_2009; bosilca\_dense\_2014]. Dense linear algebra problems are well suited to the usage of accelerators thanks to their regular pattern and the granularity of their data that can be easily adapted to the needs of a runtime system. On the contrary, sparse linear systems are very irregular, with small data of various sizes imposed by the considered problem. Thus, the benefit one can expect from the GPU on sparse linear system is not obvious and the overhead of the runtime system may be too large compared to the

<sup>&</sup>lt;sup>3</sup>Non-Uniform memory access

<sup>&</sup>lt;sup>4</sup>Single Process Multiple Data

fine granularity of the tasks. The main objective of this thesis is to study the effect of these generic runtime systems in sparse linear algebra compared to hand-tuned dedicated schedulers. Using these task-based runtime systems, we can decouple the algorithm from the architecture, and exploit accelerators in sparse direct solvers. Direct linear solvers produce a direct acyclic graph of tasks; thus, it is natural to use a task-based runtime to schedule these tasks on parallel heterogeneous clusters. Among the existing task-based runtime systems, we elected two different candidates to perform this study: STARPU and PARSEC. The proposed solutions have been validated in the sparse linear direct solver library PASTIX developed at INRIA Bordeaux - Sud-Ouest. This thesis takes place in the context of the ANR<sup>5</sup> ANEMOS project that aims at producing simulation tools for controlled plasma fusion in nuclear reactors. Among these tools, JOREK simulation code uses finite elements to discretize the domain. These elements produce elementary matrices that are used to build the global system of equation. Another objective of this thesis is to propose an efficient and easy way to assemble a distributed matrix for a sparse solver in finite element simulation codes. This thesis proposes an API that follows the original mesh parallel decomposition and is in charge of all required communications at the border of each parallel sub-domain. The API is generic and could be used above any linear solver, in any simulation code.

In the first chapter of this thesis, we describe the global framework of high performance computing. We detail the different architectures that have been developed to perform efficient computation. Then, we explain the different methods available to exploit the new heterogeneous parallel machines. Those methods that have been developed to address sparse linear systems are described, and we particularly focus on sparse direct algebra parallel solvers, which are the target of this thesis. Then, this chapter describes emerging heterogeneous architectures and how linear algebra libraries have been modified to fit these machines.

The second chapter presents how PASTIX direct solver has been modified to handle shared memory heterogeneous nodes. It introduces the PASTIX direct solver library in detail and the two task-based runtime systems used in this study: STARPU developed at INRIA Bordeaux - Sud-Ouest and PARSEC from ICL<sup>6</sup> at the University of Tennessee, Knoxville. Then, we detail the changes we have performed in PASTIX to use taskbased runtime systems and compare the performance of the new implementation with the highly tuned original static scheduler on multi-core NUMA nodes. On sharedmemory homogeneous nodes, we show performance results with the implementation of the sparse linear decomposition on top of generic runtime systems comparable to the original scheduler. Then, we provide a new kernel to the runtime system to offload the most compute intensive tasks (i.e. matrix-matrix products) on the GPUs. The heterogeneous experiments show up to 2.8 time speed up when adding three GPUs to the twelve basic cores.

In the third chapter, we tackle the problem of using the task-based runtime imple-

<sup>&</sup>lt;sup>5</sup>Agence National pour la Recherche, a French agency that provides funding for project-based research <sup>6</sup>The Innovative Computing Laboratory

mentation of PASTIX on distributed platforms of heterogeneous nodes. We present the new difficulties that arise on a distributed cluster, and we study the implementation of two different parallel algorithms on top of task-based runtime systems. We evaluate the performance of their implementations. Experiments present encouraging results on a cluster of heterogeneous node.

The fourth chapter deals with the integration of our work in JOREK, a production controlled plasma fusion simulation code from CEA Cadarache. We describe here a generic finite element oriented distributed matrix assembly and solver management API. The goal of this API is to optimize and simplify the construction of a distributed matrix which, given as an input to PASTIX, can improve the memory scaling of the application. Experiments exhibit that using this API we could reduce the memory consumption by moving to a distributed matrix input and improve the performance of the factorized matrix assembly by reducing the volume of communication.

Finally, we summarize the results obtained in the context of this thesis and propose new directions opened by these works.

## Chapter 1

# Linear algebra on modern architectures

#### Contents

| 1.1 Par | allel architectures                                                     |

|---------|-------------------------------------------------------------------------|

| 1.1.1   | Multi-core machines                                                     |

| 1.1.2   | Accelerators                                                            |

|         | 1.1.2.1 Graphical Processing Units                                      |

|         | 1.1.2.2 Intel Xeon Phi                                                  |

| 1.2 Ad  | dressing parallel machines                                              |

| 1.2.1   | Parallel programming                                                    |

| 1.2.2   | Addressing accelerators                                                 |

| 1.2.3   | Task-based runtime systems                                              |

|         | 1.2.3.1 Generic runtime systems                                         |

|         | 1.2.3.2 Runtime systems specifically designed for linear algebra        |

| 1.3 Spa | arse linear algebra methods                                             |

| 1.3.1   | Prerequisite: Basic Linear Algebra Subroutines                          |

| 1.3.2   | Solving a sparse linear system                                          |

| 1.3.3   | Description of the direct methods                                       |

|         | 1.3.3.1 Reordering of the unknowns $\ldots \ldots \ldots \ldots \ldots$ |

|         | 1.3.3.2 Symbolic factorization                                          |

|         | 1.3.3.3 Factorization methods                                           |

|         | 1.3.3.4 Triangular system solve                                         |

| 1.3.4   | Linear algebra on homogeneous clusters                                  |

| 1.3.5   | Linear algebra on heterogeneous clusters                                |

|         | 1.3.5.1 Dense linear algebra evolution                                  |

|         | 1.3.5.2 Sparse linear solver on heterogeneous machines                  |

| 1.4 Dis | cussion                                                                 |

Numerical simulations require more and more computational power to reach higher accuracy in a shorter time and desktop computers quickly expose their limits. To bypass this limit, parallel machines have been developed and keep evolving. To efficiently exploit these machines, high performance algorithms have to follow the evolution of the machines architectures. In particular, the linear system solve is one of the most intensive computational tasks of many numerical simulations and algorithms' developers have to follow closely the transformation of parallel architectures.

In this chapter, we first present the current evolution of parallel machine architectures. We describe the now common multi-core machines and the different many-core architectures proposed by the manufacturers. Then, we introduce the different techniques and languages available to address these machines efficiently. And finally, we describe how sparse linear algebra developers have recently updated their software to target those powerful and complex machines.

Once the high performance context has been set up, we look into the main subject of this thesis: "sparse linear algebra solvers." First, we describe the multiple solutions available to solve sparse linear systems, exposing the advantages and the drawbacks of each solution. After that, we specifically focus on direct factorization methods, describe the different steps they are based on, and exhibit the characteristics of each existing algorithm. Several sparse linear solvers implement these algorithms, we present them and specify the differences and advantages of each implemented methods. These solvers already handle clusters of multi-core nodes, they are now tackling the heterogeneous architectures. This chapter finally describes the techniques used to target parallel clusters and how sparse linear solvers are evolving to take into account emerging heterogeneous clusters.

### **1.1** Parallel architectures

Machines kept getting more complex to get more efficiency while using and dissipating less energy. In this section, we describe the different architectures that emerged to increase the effectiveness of our computers, specifically in the field of high performance computing. Two solutions are available to increase computational power. The simplest one is the multiplication of classical cores that will execute tasks in parallel. Then, more specialized computing units, called accelerators, were proposed besides the classical cores. This section details these heterogeneous computing environment.

#### 1.1.1 Multi-core machines

During last decade, multi-core machines have been widely generalized. Indeed, increasing transistor's frequency has not been possible anymore due to limits of thermal dissipation. Frequency has even been decreasing on some architectures to cut down the energy consumption and avoid the dissipation issues. Nowadays, the mean frequency of a processor

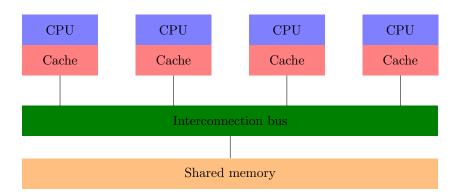

Figure 1.1 – A four CPUs SMP machine.

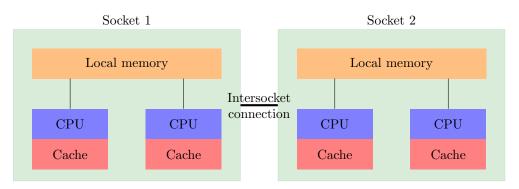

Figure 1.2 – A four CPUs NUMA machine.

is about 2.8GHz whereas it reached more than 3.5 GHz ten years ago. In order to keep increasing the computational power and follow *Moore's law* [moore1965cramming] which predict that the number of transistors in our machines double every 18 months, machines manufacturers have multiplied the computing units in our computers. This trend spread to all the market, even our phones have multi-core processors nowadays. Indeed, as the engraving sharpness keeps improving, it is possible to produce chips with more and more computational cores. We can distinguish two classes of multi-core machines.

SMP (Symmetric Multi-Processor, see Figure 1.1) machines offer a symmetric access to the memory, each core is connected equally to the memory. These machines appeared first but are almost nonexistent today. The high number of interconnection buses required limited the number of cores on a chip caused the extinction of SMP architectures. On the contrary, with their simpler design, Hierarchical NUMA (Non-Uniform Memory Access, see Figure 1.2) architectures are more scalable and flood the market. Their memory is distributed among the different processors, connected in a tree-shape structure. Adding cores in this tree is easier than in an SMP machine. With NUMA machines, the complexity is delayed to the developers.

Simultaneously to this evolution of shared memory machines, the cores' complexity

increased to accelerate computations. Today, CPU cores are integrating multiple cores and many transistors. They are capable of computing complex operations. Out-of-order execution also improved the efficiency of the computation at runtime. Modern CPUs integrate vectorial computation units, they are capable of executing the same operation simultaneously on a data vector. This vectorized operations are call SIMD instructions (Single Instruction Multiple Data). These CPUs also integrate several levels of cache memory for an optimal data management.

To get more and more computational power, machines are also connected together and work can be distributed among the different nodes. Such a group of connected computers form a cluster. Usually, a high-speed and low-latency network connects the different nodes and reduces the communication time between two nodes. The different computers in a cluster are also usually identical to avoid an additional complexity in their exploitation.

#### 1.1.2 Accelerators

Using accelerators is not a new concept in the field of scientific computing and application-specific accelerating boards have been used for decades. Yet, these dedicated boards, specially developed for specific applications, had prohibitive cost, and their distribution kept being limited. First accelerators, called ASIC (Application Specific Integrated Circuits) appear around 1980. They were specifically designed to execute a unique task with power-efficiency. In 1985 Xilinx proposed the FPGAs (Field-Programmable Gate Arrays), a flexible alternative to ASICs. They are composed of programmable logic blocks wired together using a circuit description language. Thus, FPGAs are more flexible than ASICs that are not reconfigurable, but they are also less specific and, consequently, less efficient. We can also cite ClearSpead boards which implement widely used operators and were integrating in 2006 in Tsubame Grid Cluster which reached the ninth rank of top500 [meuer\_top\_2014] ranking list. On this machine, these boards gave a 24% performance increase against a 1% additional power requirement. In any case, this kind of card did not generalize because of their high production cost. Today, the energy required to exploit a large parallel machine using classical cores became prohibitive. Large supercomputers consume much energy (e.g. 17 mega watts for the first machine of June 2014 top500) and having high Flop/s (Floating Point Operations per second) per watt processing units is a requirement. Supercomputers assemblers need both energy efficient and cheap accelerators. [krieder overview 2012] gives a quick overview of the existing accelerators available, and next paragraphs present the two of them currently available in clusters.

#### 1.1.2.1 Graphical Processing Units

The widely spread GPU cards revealed itself as a good candidate to accelerate computation. Indeed, the large video game community allows for the massive graphic boards production. Graphic cards vendors can sell billions of GPUs and economy of scale is possible. Moreover, these cards are very efficient SIMD vectorial processing units with a

Figure 1.3 – Architecture of the NVIDIA Kepler GK110.

large memory bandwidth. They can compute vectorized operations at a very high rate. Finally, these cards have a low computational power over energy consumption ratio. Noticing these advantages, few highly skilled developers diverted these graphical cards to accelerate vectorized operations. Considering this new possibility, manufacturers developed specialized chipsets and APIs to target high performance computing; GPG-PUs (General Purpose Graphical Processing Unit) emerged. In [owens\_gpu\_2008], Owens et al. describe the characteristics and possibilities of a GPU. Still, GPUs are not suitable to all types of computations and programmers started to select which part of the computation they offload to the GPU.

We call "GPU kernel" a portion of code that is going to be executed on these devices. Each instance of a kernel is run by a thread. Usually, but it can depend on the device, 32 of these threads form a block, also called a warp. An internal scheduler executes each thread within a block simultaneously, and a thread cannot communicate with threads outside the block. Each thread can have a fast access to the shared memory as long as each thread accesses a different bank (of size 16 or 32 depending on the device). A larger global memory is also available to all the blocks but with a higher latency. Thus, developers have to be very careful to manage correctly their memory accesses when writing a GPU kernel.

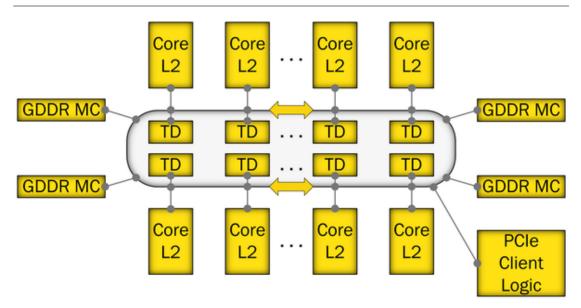

Figure 1.3 represents the NVIDIA Kepler GK110 with its 15 SMX (next-generation Streaming Processor) units and 1536KB shared L2 cache. Each SMX contains 192 single precision units, 64 double precision units, 32 SFU (Special Function Units) and

32 load/store units. Therefore, a single precision code will run three times faster than the double version. Each SMX is also equipped with 64KB memory divided into shared memory and L1 cache (48KB/16KB or 16KB/48KB).

AMD also provides GPU dedicated to high performance computing. Today, their performance is comparable to the NVIDIA GPUs, but they have had a hard time gaining market share.

#### 1.1.2.2 Intel Xeon Phi

More recently, Intel designed new accelerators to counter GPGPUs. The Intel Xeon Phi [jeffers intel 2013] also aims at reducing the energy cost of a Flop. This accelerator is less specific than a GPU. Indeed, the Xeon Phi comprises many (61 on last release) simplified classical processors. The cores are based on the well-tried P54C design (Original Pentium design). This design has been simplified to the maximum to reduce their energy cost. Figure 1.4 presents this device architecture. A very high bandwidth bidirectional ring of interconnection is linking these cores together. Each core comes with its private cache memory that is kept coherent using the global-distributed tag directory (TD). The PCIe Client Logic is managing the PCI bus (i.e. the link to the host machine) while the GDDR MC is in charge of controlling accesses to the GDDR5 (Graphic Double Data Rate, specialized memory originally used on graphic cards) memory available on the coprocessor. Each core is capable of executing four threads and has a vector processing unit executing 512 bits SIMD instructions. Developers can either off-load part of the computation to the Intel Xeon Phi, as it is done with a GPU, or execute the whole code on the coprocessor (as if it was a remote server). The later option requires the ability to compile the whole application with a dedicated compiler. To get performance from the Intel Xeon Phi, algorithms must be highly parallel and use efficiently both the 244 threads and the SIMD units.

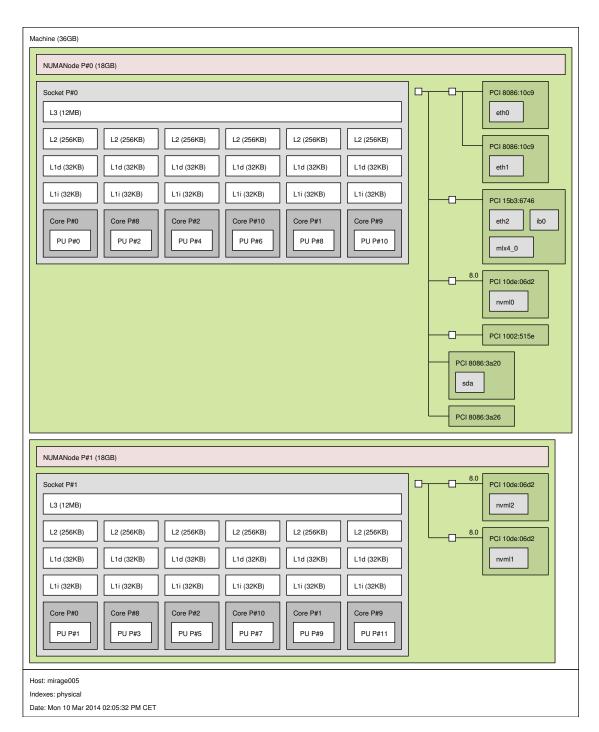

Fastest machines in the top500 ranking are clusters of distributed NUMA machines equipped with many-core devices (i.e. either GPUs or Intel Xeon Phi coprocessors). The top machine from June 2014 ranking is Tianhe-2 a Chinese cluster. Each of the 16000 nodes is equipped with two classical Intel Xeon cores, and three Intel Xeon Phi coprocessors. Figure 1.5 presents a smaller configuration, one Mirage node from PLAFRIM experimental platform in Bordeaux, which has been used in the experiment presented in chapter 2. It contains two hexa-core processors: one connected to a GPU, and the other to a pair of GPUs. Several nodes of this kind are then interconnected using a high performance network, adding an additional level to the hierarchical layout. The current challenge for developers is to use efficiently all the computational power offered by these complex architectures.

### **1.2** Addressing parallel machines

As we have seen before, to reach higher and higher computational power, machines had to integrate more and more complex hardware. It became quite hard to reach the peak

Figure 1.4 – Architecture of the Intel Xeon Phi.

performance of such a machine. To illustrate this one can have a look at the top500 ranking. Indeed, on this list we can notice the difference between the theoretical peak performance and the greatest performance obtained running the LINPACK test suite. Depending on the architecture, approaching the peak performance is harder. A solution to ease the development on such architectures is thus required. In this section, we present the different frameworks that we can use to exploit efficiently the complex architecture provided by machine manufacturers. First, we introduce the techniques available to get an efficient parallel code on a classical multi-processor machine. Then, we specifically detail solutions to implement high performance algorithms for modern accelerators.

#### 1.2.1 Parallel programming

Inside a node, several solutions were developed to implement shared memory algorithms. The solutions are identical for SMP and NUMA nodes. While high level shared memory solutions can handle NUMA effects through an intelligent runtime system [**broquedis\_dynamic\_2009**], in the general case, the developers have to adapt its algorithm. To target shared memory architectures, operating systems first proposed inter-processes memory sharing solutions. Today, they integrate lightweight processes (threads) which can be created from a master process, and share access to its memory. For example, POSIX operating systems provide P-Threads (POSIX Threads) that developers can use to handle threads accurately. With this solution, the developer has to explicitly start threads from the main process with a given task to execute. Other solutions provide simpler and higher level ways to express parallelism, hiding the underlying thread library to the developer. The most common is OPENMP [**chandra2001parallel**], a language extension, available for both Fortran and C, that handles shared memory accesses is the solution of the memory is provide for both fortran and C, that handles shared memory accesses and the memory accesses are memory and the memory are accessed to be the memory.

Figure 1.5 – A Mirage node described using Hardware Locality (hwloc) tool.

ory parallelism using threads. OPENMP proposes to annotate the code with *pragma* keywords. The simplest way to use OPENMP is to specify which "for" loops can be executed in parallel so that the runtime can execute iterations simultaneously. OPENMP also proposes the possibility to split a program into independent tasks for a more advanced usage. Intel also proposes the Intel TBB (Thread Building Blocks) library [tbb], in C++, that provides similar tools such as parallel\_for, parallel\_while, and parallel\_reduce functions, or a task-based programming API. Cilk [cilk ] proposes to extend C language to extract "fork-join" parallelism from the algorithm. The user specifies which routines are *Cilk* functions and can be executed in parallel. These selected functions can then be *spawned* and executed by parallel threads. To ensure the ending of the *spawned* functions, user has to call a *Cilk* synchronization routine. All these solutions can reach high performance if the developer describes accurately enough the parallelism of its algorithm.

To address distributed machines, the message passing paradigm is mainly used. This paradigm proposes to exchange data between different instances of one program using messages that are explicitly sent by an instance and received by another. The developer has to describe precisely the data distribution, and the way data are exchanged. One specific standard, MPI [gropp1999using] (Message Passing Interface), emerged as the elected one to handle parallel clusters. Many implementations of this standard were developed. Only MPICH [gropp mpich2: 2002] and OPEN-MPI [gabriel\_open\_2004] survived and are used by manufacturers to develop their own libraries such as Intel MPI, Bull MPI, etc. Languages extensions such as Co-Array Fortran [numrich co-array 1998], HPF [richardson high 1996] (High Performance Fortran), UPC [upc] (Unified Parallel C), and more were also developed to address distributed machines. Each language extension provides a higher abstraction of the algorithm, but MPI, which let the programmer decide exactly how its application will behave, is the most used parallel library. All these solutions can also be applied to shared memory systems (which is simpler as all processes can reach all data). Although such a solution can use optimizations to exploit the direct memory access possibilities, the message passing paradigm implies data duplication that could be avoided in a shared memory context. Indeed, threads would share the same data. However, using memory sharing and threads requires protection locks that can slow down the computation. The developer has to minimize the size of lock protected area and find a tradeoff between memory sharing and distributed implementation corresponding to its application.

In a distributed code, communications can consume a lot of time. In order to get more efficiency, the developer has to overlap the communications with computations. In a more general case, one should avoid synchronization to get performance. Indeed, when the number of computational unit increases, synchronizing the whole machine can be prohibitive. Thus, the commonly used *fork-join* parallelization scheme where sequential section and parallel section are interleaved, implying synchronization in-between, and must be avoided.

#### 1.2.2 Addressing accelerators

To off-load part of a computation to an accelerator, one would have to write a specialized kernel for the targeted architecture. The developer can either write a whole code that will be executed on the accelerator, or offload only part of the computation to the device. The second option appeared to be more efficient in many cases as the accelerators, particularly the GPUs, but also the Intel Xeon Phi, are not suited for all kinds of operations. Thus, the developer has to send the data to the accelerator, execute the kernel and retrieve the data from the device. The memory transfer cost can be very expensive and, as in a distributed code, the developer has to overlap those communications with computations.

To help in the design of applications adapted to these complex architectures, frameworks have been developed. NVIDIA proposes CUDA [nvidia inc nvidia 2011 and several organizations (Apple, AMD, Intel, and NVIDIA) promote OPENCL [stone opencl: 2010 ] to develop the kernels, handle the memory transfers, and execute the kernels on the device. Intel encourages using OPENMP [cramer\_openmp\_2012 ] to produce parallel code to target its Intel Xeon Phi. While CUDA is specific to NVIDIA GPUs, OPENCL aims at providing a portable solution to accelerators and multi-core management. In reality, if OPENCL provides portable code, most of the time the performance is not portable, and the kernels have to be redesigned to target a new architecture. The main challenges raised by these heterogeneous platforms are mostly related to task granularity and data management: although regular cores require fine granularity of data as well as computations, accelerators such as GPUs need coarse-grain tasks. This unavoidably introduces the need for identifying the parts of the algorithm that are more suitable to be processed by each kind of architecture. Using one of the presented frameworks, one can execute part of its code on an accelerator and keep the other part on the classical CPU(s). The drawback of this approach is that, except if a very complex code is written to handle it, the CPUs are idle while the GPU computes, and vice versa. A need for more flexibility is required to use the maximum power from heterogeneous nodes.

This, coupled to the solutions for shared and distributed architectures, is a large burden to the developers who want to benefit from all the capabilities of the clusters. An additional layer, which would insulate the algorithms and their developers from the rapid hardware changes, is required. This portability layer recently reappeared as under the denomination of task-based runtime. Those runtime systems are presented in next subsection.

#### 1.2.3 Task-based runtime systems

Many initiatives have emerged in previous years to develop efficient runtime systems for modern heterogeneous platforms. Task-based runtime systems propose to describe the algorithms as tasks with data dependencies in-between. The underlying runtime systems manage the tasks dynamically and schedules them on all available resources. The algorithm can then be represented as a DAG (Directed Acyclic Graph) where vertices are representing the tasks and edges their dependencies. These runtime systems can be generic, as STARPU [Augonnet\_2010\_ccpe; augonnet\_scheduling\_2011 ] and PARSEC [dague:12], or more specialized as QUARK [icl:759]. Without going into details, the main differences among these different runtime systems reside in their representation of the graph of tasks, their management of data movements between computational resources, the extent they focus on task scheduling, and their capabilities to handle distributed heterogeneous platforms.

#### 1.2.3.1 Generic runtime systems

Many different task-based runtime systems were recently developed to help developers produce efficient algorithm on heterogeneous architectures. Among them, Qilin **[Qilin** provides an interface to submit kernels that operate on arrays that are automatically dispatched among the different processing units of a heterogeneous machine. Moreover, Qilin dynamically compiles parallel code for both CPUs (by relying on the Intel TBB technology), and for GPUs using CUDA. Another relevant framework is Charm++ [Kale:1993:CPC:167962.165874] which is a C++-based parallel programming system that provides sophisticated load balancing and a large number of communication optimization mechanisms. Charm++ has been extended to provide support for accelerators such as the Cell processors as well as GPUs [charmaccel]. Runtime systems like KAAPI/XKAAPI [kaapi ] or APC+ [apc ] also offer support for hybrid platforms mixing CPUs and GPUs. Their data management is based on a DSM-like mechanism: each datum block is associated with a bitmap that permits the determination of whether there is already a local copy available to a specific processing unit or not. The STARSS project is actually an umbrella term that describes both the STARSS language extensions, and a collection of runtime systems planas hierarchical 2009 ] targeting different types of platforms [gpuss; smpss; cellss ]. STARSS provides an annotation-based language that extends C or Fortran applications to offload pieces of computation on the architecture targeted by the underlying runtime system. With STARPU [Augonnet 2010 ccpe], the user uses a generic sequential task-based programming model to insert tasks which will be executed in parallel by the different workers (i.e. computing units). The scheduler that will execute these tasks can be either chosen among the STARPU predefined ones or provided by the user as a plugin. Finally, the PARSEC [dague:12] (formerly DAGUE) runtime system dynamically schedules tasks within a node using a rather simple strategy based on work-stealing and following an initial data distribution. It was first introduced for dense linear algebra, but was later extended to more generic applications (e.g. in the high order finite element library Aerosol [mbengoue\_comparison\_2013]). It takes advantage of the specific shape of the task graphs (in the sense that there are few types of tasks) to represent the task dependency graph in an algebraic fashion as expressed in [cosnard1999compact]. Following this idea, the OPENMP consortium, supported by Intel, is developing OPENMP 4 which integrates the concept of interdependent tasks extending the task concept introduced in OpenMP 3.

#### 1.2.3.2 Runtime systems specifically designed for linear algebra

Some other runtime systems are specifically designed for dense linear algebra. For example, the TBLAS runtime system [tblas] follows a linear algebra specific approach. It automates data transfers and provides a simple interface to create dense linear algebra applications. TBLAS assumes that programmers provide a static mapping of the data on the different processing units, but it supports heterogeneous data block sizes (i.e., different granularity of computations). The QUARK runtime system [quark] was specifically designed for scheduling linear algebra kernels on multi-core architectures and is used in the PLASMA project [agullo numerical 2009]. It is characterized by a scheduling algorithm based on work-stealing and by its higher scalability in comparison with other dedicated runtime systems. Finally, the SuperMatrix runtime system [supermatrix], used by FLAME [igual\_flame\_2012] library, follows nearly the same idea as it represents the matrix hierarchically: the matrix is viewed as blocks that serve as units of data where operations over those blocks are treated as units of computation. The implementation transparently enqueues the required operations, internally tracks dependencies, and then executes the operations using out-of-order execution techniques.

### **1.3** Sparse linear algebra methods

The scientific community has developed multiple methods to efficiently solve sparse linear systems of the form Ax = b, where A is a sparse matrix of size n. A is said to be a sparse matrix if it contains only few non zero terms. This low fill-in is owed to either nonexistent or neglected interactions in the mathematical model used by the simulation. Indeed, coefficients of the matrix usually represent the interactions between two points resulting from the discretization of the studied problem. Frequently, interactions between two remote points can be neglected and zero terms appear in the matrix. x and b are two n sized vectors. x is the unknown of the system to be solved and b is called the right-hand-side. x can then be obtained with the formula  $b = A^{-1}x$ .

To illustrate this, we can consider the air flow around a plane. One can consider that the characteristics of the air flow at the end of the left-wing would have only little influence on the flow on the right-wing. The corresponding term in the matrix would then be null. If we keep following the air flow simulation example, x would be the air flow speed at time t + 1, computed from b, the air flow speed at time t.

However, the computation of the matrix  $A^{-1}$  is generally avoided. Indeed, we have no a priori knowledge of the structure of  $A^{-1}$ , and it might require being stored in an expensive dense matrix. This computation would require too much memory and computational time. The scientific community developed many other methods to obtain the solution x. These methods are adapted to the characteristics and the constraints of the simulation code. Indeed, the need for accuracy, the structural and numerical stability of the matrix at each time step, and its numerical complexity depend on the studied problem and the method used for the simulation. Two main classes can be distinguished to solve sparse linear systems: direct methods and iterative methods. These sparse linear algebra methods rely on the BLAS (Basic Linear Algebra Subroutine) libraries that we will present in next section. Then, we will exhibit the advantages and drawbacks of the existing methods. After that, we will focus on direct methods that are the main topics of this thesis. We will explain

the different steps involved in a direct sparse linear solver. Finally, we will compare the multiple implementations available and show how they started addressing heterogeneous machines.

### 1.3.1 Prerequisite: Basic Linear Algebra Subroutines

Independently of the method, if the computational intensity is not too low, operations have to be gathered into dense blocks to be efficient. For example, in MATLAB (a widely used numerical computing environment), a BLAS-based method is used to solve Ax = b when the ratio between the number of operations and the number of entries in the matrix is smaller than 40. Otherwise, a scalar method is used. Indeed, dense matrixmatrix operations can be computed very efficiently on computing unit whereas memory accesses are limiting the efficiency of sparse operations. These operations have to be adapted to the structure of the computing unit to use its different level of cache memory efficiently. The BLAS [blas ] API became the standard to handle these operations. The API defines three classes of operation:

- BLAS1: for scalar, vector and vector-by-vector operations (O(n) operations for O(n) data);

- BLAS2: for matrix-by-vector operations  $(O(n^2) \text{ operations for } O(n^2) \text{ data})$ ;

- BLAS3: for matrix-by-matrix operations ( $O(n^3)$  operations for  $O(n^2)$  data).

As they involve more computations, the BLAS3 operations are the ones that benefit most from a precise tuning of the algorithm. Among the multiple implementation of the BLAS API, we can cite several implementations.

- **refblas** [**blas1**; **blas2**] is the reference implementation from netlib. This implementation must be avoided to obtain performance.

- ATLAS [atlas; atlas1] (Automatically Tuned Linear Algebra Software) is an open source implementation that relies on automatic tuning, and thus available for all CPU architectures.

- MKL [mkl ] (Math Kernel Library) is the Intel implementation mainly dedicated to Intel processors.

- ACML [acml] (AMD Core Math Library) is the AMD implementation of the BLAS API.

- ESSL [kagstrom\_gemm-based\_1998 ] (Engineering and Scientific Software Library) is IBM's implementation.

**OpenBLAS** [goto ] (Formerly GotoBLAS) originally developed by Kazushige Goto relies on TLB (Translation Lookaside Buffer) misses optimization instead of cache misses.

These implementations are finely tuned to fit perfectly the characteristics of the machine they are executed on and get the maximum performance from the chipset [eddelbuettel\_benchmarking\_2010]. To address SMP and NUMA machines, multi-threaded versions of these libraries were developed such as for ACML, MKL or OPENBLAS [goto2]. Distributed versions of these libraries are also available. For example PBLAS [choi1996proposal] provides a distributed implementation of the BLAS2 and BLAS3 routines. LAPACK [anderson\_lapack\_1999], and SCALA-PACK [scalapack], on distributed memory clusters, use the classical BLAS routines and provide higher level routines such as dense linear decomposition, eigenvalues problems, etc.

#### 1.3.2 Solving a sparse linear system

Direct methods [davis direct 2006] consist in the decomposition of the matrix A in a product, LU, of two triangular matrices. The first one, L, is lower triangular where the other one, U, is upper triangular. Once it has been transformed into LUx = b, the system can then be simply decomposed in two triangular systems easy to solve. If the matrix has specific properties, the problem can then be further simplified, often in term of computational cost. For example, in the symmetric positive definite (SPD) case, the Cholesky factorization gives  $A = LL^T$ . If A is only symmetric, it is still possible to achieve a Cholesky-Crout decomposition:  $A = LDL^T$ , where D is a diagonal matrix. These last two decomposition methods reduce by half the computational and memory costs. Using direct methods, one can get a very accurate solution of the Ax = b system. Moreover, once the decomposition is computed, it can be used to solve several systems where only the right-hand-side would differ. The drawback of these methods is that they require a huge amount of memory, which can be a bottleneck preventing the increase of the solved system size. Indeed, during the decomposition, new non-zero terms, called fillin, appear in the matrix, increasing the memory requirement. This phenomenon is more detailed in subsection 1.3.3. A second bottleneck is the complexity of the decomposition algorithm, which is very large:  $O(n^3)$  operations for a dense factorization,  $O(n^{\frac{3}{2}})$  for a 2D sparse decomposition and  $O(n^2)$  for a 3D sparse factorization.

Iterative methods are a cheaper alternative to the direct methods, both in terms of memory and complexity. They solve the equation Ax = b from an initial guess  $x_0$  that is iteratively improved at each iteration until the inquired precision is reached. In [saad96], Youssef Saad presents a large diversity of iterative methods (e.g. GMRES, Conjugate Gradient, etc.). These methods are cheap both in term of memory and computational time. They are generally based on the matrix-vector product that can be computed in O(nnz), where nnz is the number of non-zero terms in the matrix. To reach the precision of a direct method, a large number of iterations (or a very accurate initial guess) would be required. However, in many simulations a fine accuracy is not required, and iterative

methods can be a good candidate. Depending on the complexity of the studied problem, an iterative method can be unable to converge to the solution. Indeed, the behavior of iterative methods is specific to the problem they are trying to solve. The convergence of these algorithms also relies on a good choice of the initial guess  $x_0$ .

For solving 3D problems, where the matrix A is quite dense, iterative methods are generally more interesting because of their low computational cost. On the contrary, 2D problems lead to rather sparse matrices that will not fill-in too much during the decomposition. Direct methods are then well suited for these problems.

Transitional solutions were proposed to exploit the best of the two methods. The first possibility is to approximate the decomposition of the matrix A. For instance, it is possible to suppress some values considered negligible or to ignore the *fill-in* terms that appears during the decomposition. Those methods are called incomplete LU decompositions. The selection of the terms to remove is either based in value threshold (ILU(t) methods [saad\_ilut:\_1994 ]), or on their level of interconnection (ILU(k) methods [manteuffel\_incomplete\_1980 ]). This level is defined as follows: level zero comprises initial terms and level k ( $k \ge 1$ ) terms are fill-in terms generated by the updates involving level k - 1 terms. With these methods, we get an approximation of A's decomposition that is used as a preconditioner P for an iterative method. Then, for a left preconditioning, one solves  $P^{-1}Ax = P^{-1}b$  which leads to a better convergence. One can also use a partial factorization as a preconditioner. This is the method used by the JOREK application studied in this thesis and presented in chapter 4.

To reach larger problems while keeping a high accuracy, one can use domain decomposition methods. These algorithms split the problem into sub-domains, solve independently the problem with a direct method on the interior of each sub-domain while reporting the contribution to the Schur complement (i.e. the local interface), and, finally, solves iteratively a global system on the interfaces. HIPS [gaidamour\_parallel\_2008 ], MAPHYS [giraud\_parallel\_2009 ], PDSLIN [yamazaki\_pdslin\_2012 ], and SHYLU [rajamanickam\_shylu:\_2012 ] implement these domain decomposition methods in different ways. PDSLIN and SHYLU use a twofold approach to compute the preconditioner. First, an approximation to the global Schur complement is computed. Then, this approximation is factorized to form the preconditioner for the Schur complement system that does not need to be formed explicitly. HIPS builds its preconditioner using an Incomplete LU factorization while MAPHYS computes an additive Schwartz preconditioner. All these methods try to benefit both from the speed and good scalability of the iterative methods, and from the accuracy and robustness of direct method.

Finally, multi-grid methods [hackbusch\_multi-grid\_1985] speed-up the performance of an iterative method by correcting, from time to time, the solution. The solution is projected onto a coarse mesh, a direct method solves the coarse problem, and then the correction is reported to the finer original mesh. The multi-grid methods can be separated into two sub-classes: geometric [hulsemann\_parallel\_2006], where the multilevel hierarchy is tightly linked to the mesh geometry and the partial differential equations; and algebraic [brandt\_algebraic\_1986], where the solver uses only the matrix and can be used as a black box.

Thus, various methods have been developed to solve Ax = b equation. The choice of the method depends on the characteristics and the needs of the simulation. Direct methods are the most robust, can be unavoidable in certain cases, and is an essential component to many other solutions. In our case, we will focus on high accuracy of direct methods which is a requirement for many simulation codes such as JOREK. We will now describe more precisely these methods and the techniques that improve their efficiency.

#### **1.3.3** Description of the direct methods

Direct methods are the central subject of this thesis. These methods are the most expensive both in term of memory and computational power. However, as we have explained, they are widely used because they can reach a very high accuracy. They can also be used as a preconditioner for hybrid methods, mixing direct and iterative methods to obtain a tradeoff among speed, accuracy, and memory consumption. The possibility to save and reuse the decomposition can also reduce the computational cost by computing the factorization only once to solve multiple linear systems sharing the same matrix A. We will see later how we can control the memory consumption of direct solvers. We will also describe the algorithms, and the parallelization techniques used to obtain efficient computation. Four main steps compose the direct methods:

- 1. The reordering of the unknowns can reduce the *fill-in* that appears during the decomposition.

- 2. The symbolic factorization that predicts the structure of the factorized matrix. Analysis of this symbolic factorization predicts the amount of memory, and the number of operations required to perform the decomposition.

- 3. The numerical factorization that computes the decomposition of A into  $L \times U$ . It is the most expensive step.

- 4. The forward/backward substitutions that compute the solution x of the system using the factorized matrix and the right hand side b.

#### 1.3.3.1 Reordering of the unknowns

For the sake of simplicity, we consider here the  $LL^T$  decomposition, when the matrix is SPD. The algorithms are easily adaptable to obtain an  $LDL^T$  decomposition by modifying the computation on the diagonal. In a general case, to obtain an LU factorization, one can consider A', the matrix obtained by completing A with zeros such that the non-zero pattern of A' is symmetric (i.e.  $pattern(A') = pattern(A + A^T)$ ). Once this matrix is constructed, the LU factorization can be obtained by performing the symmetric operations on the upper part of the matrix.

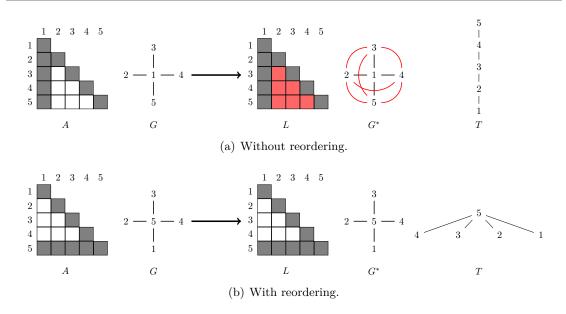

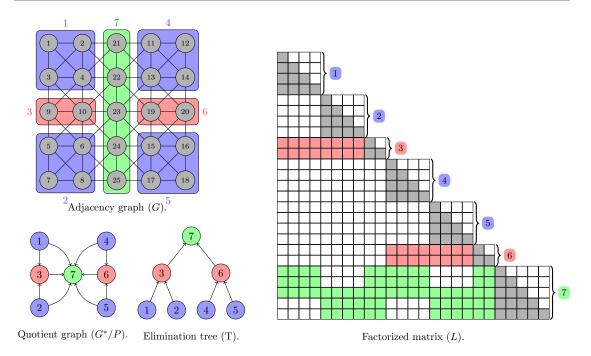

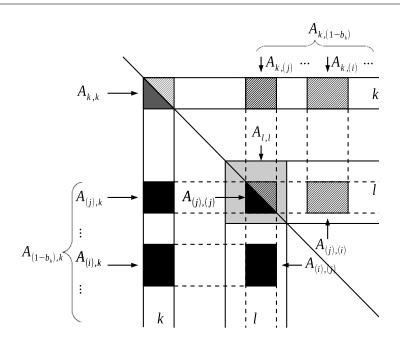

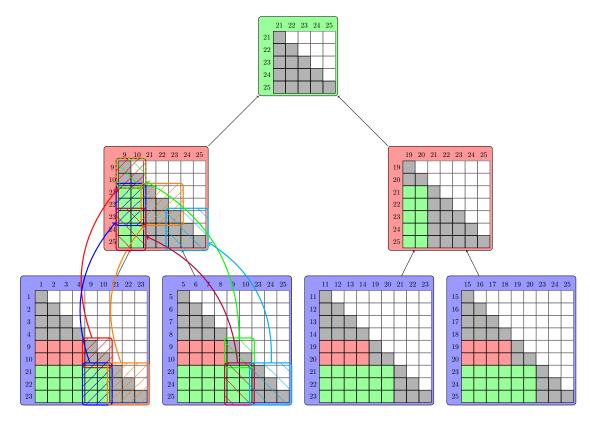

During the decomposition of the matrix A into  $LL^T$ , fill-in [r17] terms will appear. Indeed, after a Cholesky decomposition, the matrix L hold more terms than the matrix A. A crucial tool to study this fill-in is the graph model  $[\mathbf{r17}]$  associated to the Gaussian elimination. This fill-in is directly linked to the ordering of the unknowns. Therefore, we are looking for an ordering of the unknowns, that is to say an ordering of the initial matrix associated graph vertices [amdadu96; r17; pero97a; peroam99a ] that minimizes the fill-in, and simultaneously, the number of operations required to perform the decomposition. Figure 1.6 illustrates the fill-in related problems. In the case presented here, fill-in terms, in red, can be suppressed using a good reordering (Figure 1.6(b)). This minimization (or eventually, suppression in the given example) of the fill-in reduces both the storage size of the L matrix, and the number of operations to perform. Indeed, only non-zeros values of  $LL^T$  are stored and require computations.

The undirected graph G associated with a symmetric (or structurally symmetric) n by n matrix A is a graph with n vertices where there is an edge (i, j) between the vertices i and j if, and only if,  $a_{ij}$  is not null.

$$\exists (i,j) \in G \Leftrightarrow a_{ij} \neq 0$$

The elimination graph is the graph  $G^*$  associated to the lower triangular matrix L resulting from the factorization. Naturally,  $G^*$  has the same number of vertices as G but (many) more edges. Indeed, it contains the fill-in edges (in red on Figure 1.6(a)). The fill-in of the matrix can be computed using the following theorem:

#### Theorem 1 (Characterization Theorem [rose1976algorithmic])

$$(i,j) \in G^* \Leftrightarrow \begin{cases} (i,j) \in G \\ or \\ \exists a \text{ path } (j,k_1,\ldots,k_l,i) \text{ such that } \forall p \in \llbracket 1,l \rrbracket, k_p < \min(i,j) \end{cases}$$

The *Elimination tree* T [**r87**] associated to the factorized matrix is a tree (in the classical meaning of the graph theory, in the case of reducible matrix it is a forest) with n vertices. There is an edge between the vertices i and j if, and only if, the row of the first non null off-diagonal term in column j in the factorized matrix is i.

The elimination tree is crucial for sparse direct solver parallelization because it describes the dependencies among the computations: if two vertices are on different branches of the elimination tree, then the corresponding unknowns can be eliminated independently in parallel.

In a parallel context, the reordering of the vertices of G should then both minimize the fill-in, and maximize the independence of the computations during the factorization, that is to say leading to large and low height elimination trees. Following these criteria, the efficient reordering are based on minimum degree [amdadu96; tiwa67] and nested dissection [r17]. One can notice that the classical Cuthill-McKee [CutKee] reordering must be discarded because it creates more fill-in, and produces very high elimination trees with little independence among the computations. Figure 1.6 shows that a good reordering can both decrease fill-in and exhibit more parallelism.

Figure 1.6 – Advantage of reordering the unknowns for sparse matrix decomposition. Blank squares represent zeros, greys are initial non-zeros and red squares and edges the fill-in.

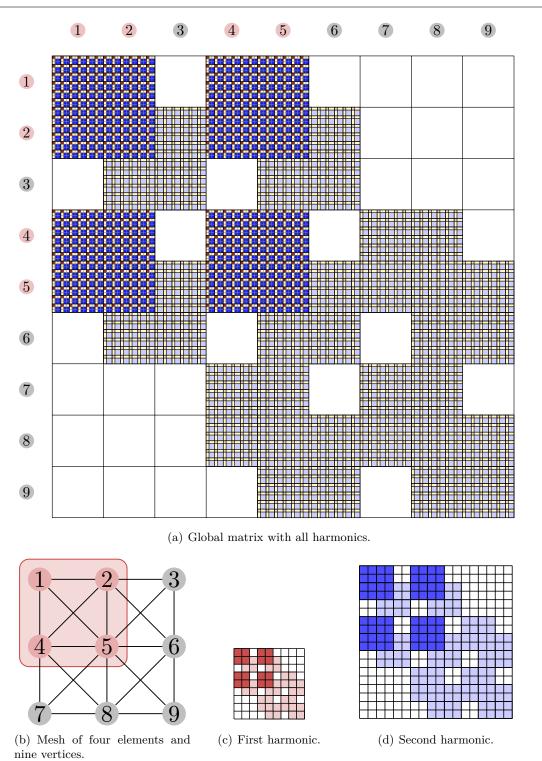

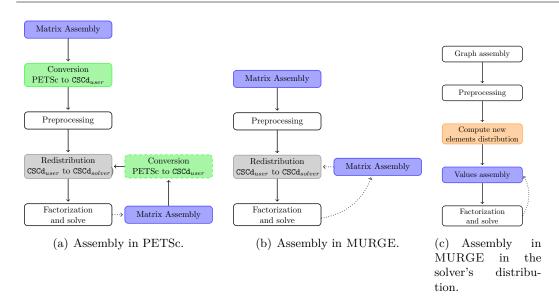

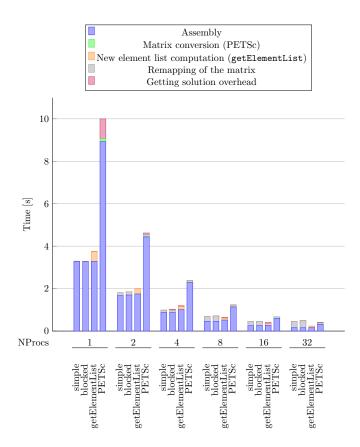

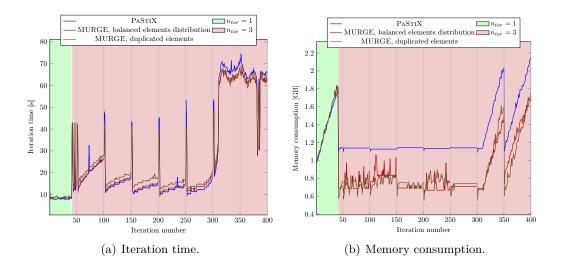

#### 1.3.3.2 Symbolic factorization