## HABILITATION A DIRIGER DES RECHERCHES

# de l'UNIVERSITÉ de VERSAILLES ST QUENTIN-EN-YVELINES

Spécialité : Informatique

présentée par

## Denis BARTHOU

Contributions à l'optimisation de code et à la génération de bibliothèques hautes performances.

Soutenue le 18 Février 2008 devant le jury composé de :

| François | Bodin      | Rapporteur  |

|----------|------------|-------------|

| David    | Padua      | Rapporteur  |

| Sanjay   | Rajopadhye | Rapporteur  |

| Albert   | Cohen      | Examinateur |

| Michael  | Gerndt     | Examinateur |

| William  | Jalby      | Examinateur |

Habilitation préparée à l'Université de Versailles -  $S^t$  Quentin au sein du laboratoire Parallélisme Réseaux Systèmes Modélisation (PRiSM)

## Résumé

Le nombre de transistors des processeurs, ainsi que leur fréquence, ont suivi la loi de Moore pendant plusieurs décennies, au prix d'une complexité croissante des architectures. La fin récente de l'accroissement en fréquence a notamment deux conséquences: le parallélisme est désormais un des seuls vecteurs de gain de performances, et la chaine de compilation ainsi que le système d'exploitation sont indispensables pour l'obtention automatique de ces performances. Dû à la complexité des mécanismes architecturaux difficiles à modéliser de façon réaliste, les compilateurs restent cependant loin de pouvoir générer automatiquement des applications hautes performances, même pour un seul core.

Le travail que nous présentons se focalise sur d'une part l'optimisation et la génération de bibliothèques hautes performances et leur réutilisation automatique dans un contexte applicatif, d'autre part, sur l'évaluation et la modélisation des performances afin de guider l'optimisation. Les résultats de ces travaux sont suivis de perspectives de recherche.

## Abstract

The number of transistors as well as the frequency of processors have followed Moore's law for the past decades, at the expense of an increase in architecture complexity. As improvements in processor clock frequencies have levelled out, a major shift to parallelism is taking place. Parallelism is now the only way to enhance performance, and compilers and operating systems are essential to improve performance automatically. Due to the complexity of hardware mechanisms, hard to model, compilers are still far from being able to generate high performance application codes, even on a single core.

The work presented in this thesis focuses on two aspects of this issue: we first describe results obtained for the optimization and generation of high performance libraries and their automatic reuse in applications, and then describe performance evaluation techniques and tools to guide the optimization process. Results of this work is followed by research perspectives.

# Contents

| 1        | Inti              | Introduction                                         |                 |  |  |

|----------|-------------------|------------------------------------------------------|-----------------|--|--|

|          | 1.1               | Performance Modeling and Phase Ordering Problem      | 10              |  |  |

|          | 1.2               | Towards a Model for Phase Ordering Problem           | 11              |  |  |

|          | 1.3               | Towards a Model for Best Optimization Parameters     | 14              |  |  |

|          | 1.4               | Outline of the Document                              | 16              |  |  |

| 2        | Dof               | actoring with Performance Libraries                  | 19              |  |  |

| 4        | 2.1               | Introduction                                         | 19              |  |  |

|          | $\frac{2.1}{2.2}$ | Program Equivalence                                  | 21              |  |  |

|          | $\frac{2.2}{2.3}$ | Finding Slices similar to Template                   | $\frac{21}{21}$ |  |  |

|          | $\frac{2.3}{2.4}$ | Exact Template Instantiation                         | $\frac{21}{23}$ |  |  |

|          | $\frac{2.4}{2.5}$ | Rewriting Code with Library Calls                    | $\frac{25}{25}$ |  |  |

|          | $\frac{2.5}{2.6}$ |                                                      | $\frac{25}{27}$ |  |  |

|          |                   | Program variations detected                          | 28              |  |  |

|          | 2.7               | Related Works                                        |                 |  |  |

|          | 2.8               | Experimental results                                 | 29              |  |  |

|          | 2.9               | Conclusion                                           | 30              |  |  |

| 3        | Lib               | brary Generation with Hierarchical Compilation       |                 |  |  |

|          | 3.1               | Introduction                                         | 33              |  |  |

|          | 3.2               | Representing Multiple Program Versions               | 35              |  |  |

|          | 3.3               | Hierarchical Kernel Decomposition                    | 37              |  |  |

|          | 3.4               | Kernel Composition                                   | 40              |  |  |

|          | 3.5               | Application on Linear Algebra Codes                  | 43              |  |  |

|          | 3.6               | Application on Large Applications                    | 46              |  |  |

|          | 3.7               | Related Works                                        | 49              |  |  |

|          | 3.8               | Conclusion                                           | 50              |  |  |

| 4 Ass    |                   | essing and Improving Compiler Generated Code Quality |                 |  |  |

| •        | 4.1               | Introduction                                         | <b>53</b> 53    |  |  |

|          | 4.2               | Modular Assembly Quality Analyzer and Optimizer      | 54              |  |  |

|          | 4.3               | Assembly Specialization Opportunities                | 58              |  |  |

|          | 4.4               | Compositional Loop Specialization                    | 61              |  |  |

|          | 4.5               | Hybrid Specialization                                | 66              |  |  |

|          | 4.6               | Related Works                                        | 70              |  |  |

|          | 4.7               | Conclusion                                           | 74              |  |  |

|          | 4.1               | Conclusion                                           | 14              |  |  |

| <b>5</b> | Per               | rspectives                                           |                 |  |  |

|          | 5.1               | Performance Modeling                                 | 77              |  |  |

|          | 5.2               | Libraries and Optimizations                          | 78              |  |  |

|          | 5.2               | Daralloliam                                          | 20              |  |  |

# Chapter 1

# Introduction

This is a great time for High Performance Computing, in particular in the compilation field.

For the last decades, the semi-conductor industry for non-embedded systems has increased processor performance by increasing clock frequency and adding a limited degree of parallelism (through small vectors and instruction level parallelism). Raising clock frequency has one overwhelming advantage: With no modification of the code, provided the programming ISA remains backward-compatible, an application runs faster just by upgrading the hardware. The price to pay is higher hardware complexity due to the slower evolution of frequencies for memories than for processors: A hierarchy of caches and a set of complex mechanisms (prefetches, out of order execution, speculation to name a few) are necessary to fill processor pipelines and sustain high performance. However the technology seems to have reached a limit due to the underlying physics: the increase in frequency is associated with CPU die shrinkage and at the atomic scale this leads to electrical leakage, responsible for excess heat generation and power consumption, important production costs....

As improvements in processor clock frequencies have levelled out, a major shift to parallelism, in particular to many-core parallelism is taking place. The only way to increase performance is to enhance parallelism, placing several processor cores on each chip. In contrast to increases in clock frequency, performance improvement on parallel machines depends essentially on parallel compilers, libraries and operating system. This is because each core is no more powerful than a traditional processor; the performance improvements come from using more than one core at the same time, and are obtained through the efficient interaction between tasks partitioning computation and data. However, generating high performance codes still remains quite challenging and is usually more complex than running in parallel efficient sequential codes. From a compiler perspective, generation of an effective parallel application requires at least three main ingredients:

- expression or detection of the parallelism

- code optimization and generation

- realistic architecture and performance model.

We briefly discuss the main issues concerning these ingredients.

Parallelism detection and dependence analysis have been under study for many years. While automatic parallelization has not met its promises, the efforts dedicated to the automatic detection of parallelism have led to efficient dependence analyses working on regular or irregular codes, for scalar, arrays and pointers (with alias analysis). Dependence analyses can exhibit parallelism that corresponds to a data-flow formulation of the sequential program, such as SSA form for scalars for instance, or single assignment form for arrays. The degree of parallelism detected is however limited: by dependence abstractions (constant distances, affine relations, ...) and by the implicit data-flow parallelism of the underlying sequential algorithm. In particular, finding parallelism in expressions, based on semantic properties of the operators, requires rewriting techniques that are out of reach of dependence analysis alone. Data-flow or stream-based languages (Khan network languages, Stream-IT [145, 69], Lustre [75], ...) explicit the flow of values, naturally associated

with a partial execution order corresponding to parallelism. The limits are still the same, no semantics of the operators, dependences constrained by language, but writing applications with explicit data-flow is assumed to favor parallel codes. Parallel languages with explicit parallelism, such as openMP or MPI let the user design its application from an algorithmic point of view and at the same time explicit coarse-grain parallelism. Finally, libraries and domain-specific languages (DSL, such as Matlab or SPL [129]) abstract away parallelism in order to focus only on the semantics of the functions. The concrete implementation of a function may be parallel or not and a multi-versioned code is able to select the best code depending on execution context and semantic properties of the algorithms. All these approaches to parallelism expression are well-known and are usually combined altogether: for instance, explicitly parallel or data-flow languages are used to express task parallelism, automatic parallelization finds instruction level parallelism and vector code, and parallel libraries are assumed to be used adequately. As Amdahl's law predicts, once parallelism is expressed, the resulting performance comes from the overhead induced by parallel constructors, and by sequential code optimizations.

Automatic code optimization and generation is usually achieved through a sequence of code transformations. While the effects of each transformation is well-known and there are transformations proposed to take advantage of each hardware mechanism, compositions of transformations have effects that are not very well evaluated. First of all, the difficulty arises from the phase-ordering problem, deciding which sequence of optimization to apply. This leads to the situation where optimization sequences are driven, in state-of-the-art compilers by heuristics. While this heuristics achieve good results in general, they show their limits for performance demanding codes and are not appropriate for the generation of high performance applications. For this reason, compilers propose pragmas and flags for the user to guide the optimization process according to the application. The difficulty also comes from the fact that architectures make the generation of high performance codes harder: many hardware mechanisms necessary to fill processor pipelines are fully controlled by the hardware, and their implementation on specific architecture is generally opaque. With these conditions, the impact of code transformations are difficult to assess precisely.

The consequence of increasingly complex hardware and optimization is that many optimizations are no longer beneficial for all programs and all inputs. In order to decide whether an optimization is worth applying or not, there is a need for a cost/benefit evaluation. This evaluation can be achieved through a performance model, experimental measures, or both. For performance sensitive to input, multi-versioned programs can overcome this difficulty and switch from one version to the other according to input values. Computing the point from which to switch to another version also requires performance evaluation according to input values. State-of-the art compilers only resort to performance model and a limited set of experimental measures through profiling, due to a limited amount of compilation time. On the contrary, iterative compilation is a pragmatic approach based on experimental search for library and application performance tuning. This exploration is guided by a performance model, by algorithmic knowledge of the application and can be limited by a finite set of compiler flags, of tile sizes values, . . . The inherent limitation of experimental search comes from the fact that executions for some input data sets are assumed to be representative of executions for any other input data. The best performing code selected is assumed to be among the best performing code for all possible input data. This assumption requires at least algorithmic knowledge and a good performance analysis.

This is one of the challenges for compilers in the many-core era: at a time where the compiler chain is essential for performance improvements, the legacy of Moore's law of the last decades has widen the gap between machine models and real machines, making harder the automatic generation of high performance codes. One answer would be to simplify the real architecture to the point where it is possible to have a performance model for it. A more realistic approach is to use an empirical search on possible optimizations, guided by a simplified model. Auto-tuning methods for library generation, such as ATLAS, Spiral, FFTW or Staple, have shown the benefits of such approach. They combine algorithmic knowledge, performance analysis with empirical search and generate high performance codes, closing the gap with hand-tuned code. Generalizing this approach to other algorithms and libraries is still an open issue. Recent papers (known as the Berkeley view [10]) propose to focus the development of auto-tuning library generators for 13 categories of computing/communication patterns and algorithms defined as dwarves, that are essential building blocks for performance intensive applications. The old principle in software engineering that good code should

be reused instead of being rewritten from scratch led to the design of many libraries, but the hypothesis associated with dwarves goes a step further. The goal is that all applications are written as compositions of patterns/algorithms coming from dwarves, and the application performance is driven by performance of dwarf functions/templates.

This habilitation thesis focuses on the problem of automatic code optimization and performance evaluation, in particular in an environment with high performance libraries. Optimizing applications with high performance libraries can be considered as a divide-and-conquer approach to the optimization problem: some parts of the application are optimized independently of the application context. Then the whole application, using these already optimized code fragments, is in turn optimized. The work described in this document tackles two issues:

- How to divide the optimization problem? So far, the choice of the program computation to implement from scratch and to take from a library is left to the developer. The decision is made from an algorithmic perspective, based on a limited choice of predefined algorithmic building blocks proposed by libraries and used by many applications. Obviously this approach does not scale well as soon as the number of functions proposed by libraries increases. The developer has to spend more time finding library functions that correspond to parts of the applications, and usually there are several possible solutions (a classical example is the computation of a convolution, written either directly or by a simpler computation in the frequency domain). This is not an issue as far as libraries are only considered for code reuse, but this is a problem when performance is concerned. For BLAS for instance, the library interface was designed by hand and counts a small number of functions. In contrast, the more recent library generator SPIRAL is able to generate highly tuned parallel code, using algorithmic knowledge, for any formula on a set of predefined operators. Deciding which part of an application correspond to a computation that SPIRAL can handle is tricky, to say the least. Moreover, SPIRAL has shown that the choice of the application decomposition into predefined operators is as important as the optimization of the operators themselves. Likewise, the dwarf approach is fundamentally based on a hierarchical decomposition (parallel templates/patterns using sequential components) and multiple decomposition will be possible for the same code. This evolution requires a more automatic approach to divide an application between libraries and developer code. We propose methods for automatic refactoring of code fragments using predefined library functions and methods for the definition of new library functions, through a hierarchical compilation of application codes. This is not opposed to the traditional of approach of libraries for code reuse. This only means that it may be necessary to change the decomposition proposed by the developer, for performance reasons.

- How to evaluate performance? The obvious way is to measure code performance for some input data but this only gives a very partial image of performance. While applications may have a small number of different input data sets (training sets for SPEC benchmarks for instance), libraries must exhibit performance for all possible valid input values. The other method for performance evaluation is based on static analysis of the code generated. This is very complex due to the large number of hardware mechanism that may impact performance and to the difficulty to have a valid and detailed model for them.

We propose combinations of measures and model in two cases. In the context of optimization using many versions, we measure performance of particular functions, called *constant performance kernels*, and use performance model on applications that are decomposed into these kernels. The idea is to ensure good performance prediction in order to generate multi-versioned codes, based on only a few experimental measures. For a more general problem of performance tuning, we propose techniques and tools combining static performance analysis and dynamic performance evaluation. Comparisons of static/dynamic performance evaluations help in identifying performance problems and guide the optimization process.

The performance evaluation problem is fundamental in the optimization process. We focus in the rest of the chapter on performance model issues and the consequences for the generation of high performance codes. Some related works concerning performance modeling and possible solutions for the phase ordering problem are first presented, then two theoretical formulations are proposed, one for the phase ordering problem, the other for the problem of finding the best parameters for a sequence of optimizations. The theorems resulting from these formulations draw hard limits on optimizations and in particular, on library generation, using empirical search. This corresponds to the context of the work presented in this document.

## 1.1 Performance Modeling and Phase Ordering Problem

Program performance modeling and estimation on a certain machine is an old (and is still) an important research topic aiming to guide code optimization. The simplest performance prediction formula is the linear function that computes the execution time of a sequential program on a simple von-Neumann machine: it is simply a linear function of the number of executed instructions. With the introduction of memory hierarchy, parallelism at many level (instructions, threads, process), branch prediction and speculation, performance prediction becomes more complex than a simple linear formula. The exact *shape* or the nature of such function and the parameters that it involves are two unknown problems until now. However, there exist many articles that try to define approximated performance prediction functions:

- Statistical Linear Regression Models: the parameters involved in the linear regression are usually chosen by the authors. Many program executions or simulation through multiple data sets allow to build statistics that compute the coefficients of the model [3, 55].

- Static Algorithmic Models: usually, such models are algorithmic analysis methods that try to predict a program performance [27, 105, 154, 143]. For instance, the algorithm counts the instructions of a certain type, or makes a guess of the local instruction schedule, or analyzes data dependencies to predict the longest execution path, etc.

- Comparison Models: instead of predicting a precise performance metric, some studies provide models that compare two code versions and try to predict the fastest one [86, 150].

Of course, the best and the most accurate performance prediction is the Turing machine itself, since it executes the program and hence we can directly measure the performance. This is what is usually used in iterative compilation and library generation for instance. The main problem with performance prediction models is their aptitude to reflect the real performance on the real machine. As well explained by Rai Jain [82], the common mistake in statistical modeling is to trust a model simply because it plots a *similar* curve compared to the real plot. Indeed, this sort of experimental validation is not correct from the statistical science theory, and there exist formal statistical methods [82] that check if a model fits the reality. Until now, we have not found any study that validates a program performance prediction model using such formal statistical methods.

Finding the best order in optimizing compilation is an old problem. The most common case is the dependence between register allocation and instruction scheduling in instruction level parallelism processors as shown in [62]. Many other cases of inter-phase dependencies exist, but it is hard to analyze all the possible interactions [158]. Click and Cooper in [33] present a formal method that combines two compiler modules to build a *super*-module that produces better (faster) programs than if we apply each module separately. However, they do not succeed to generalize their framework of module combination, since they prove it for only two special cases, which are constant propagation and dead code elimination. In [93], the authors use exhaustive enumeration of possible compilation sequences (restricted to a limited sequence size). They try to find if any "best" compilation sequence emerges. The experimental results show that, unfortunately, there is not a winning compilation sequence. We think that this is because such compilation sequence depends not only on the compiled program, but also on the input data and the underlying executing machine. In [139], the authors target a similar objective as in [33]. They succeed to produce super-modules that guarantee performance optimization. However, they combine two analysis passes followed by a unique program rewriting phase. In our work, we try to find the best combination of code optimization modules, excluding program analysis passes (unless they belong to the code transformation modules). In [168], the authors evaluate by using a performance model the different optimization sequences to apply to a given program. The model determines the profit of optimization sequences according to register resource and cache behavior. Optimizations consider only scalars and the same optimizations are applied whatever be the values of the inputs. Here, we assume on the contrary that the optimization sequence should depend on the value of the input (in order to be able to speak about the optimality of a program).

Finally, there is the whole field of iterative compilation. In this research activity, looking for a good compilation sequence requires to compile the program multiple times iteratively, and at each iteration, a new code optimization sequence is used [41, 150] until a "good" solution is reached. In such frameworks, any kind of code optimization can be sequenced, the program performance may be predicted or accurately computed via execution or simulation. There exist other attempts that try to combine a sequence of high level loop transformations [34, 160]. As mentioned, such methods are devoted to regular high performance codes and only use loop transformation in the polyhedral model.

# 1.2 Towards a Model for Phase Ordering Problem

We present in this section a theoretical framework about the phase ordering problem. Let  $\mathcal{M}$  be a finite set of program transformations. We would like to construct an algorithm  $\mathcal{A}$  that has three inputs: a program  $\mathcal{P}$ , an input data I and a desired execution time T for the transformed program. For each input program and its input data set, the algorithm  $\mathcal{A}$  must compute a finite sequence  $s = m_n \circ m_{n-1} \circ \cdots \circ m_0$ ,  $m_i \in \mathcal{M}^*$  of optimization modules<sup>1</sup>. The same transformation can appear multiple times in the sequence, as it occurs already in real compilers (for constant propagation/dead code elimination for instance). If s is applied to  $\mathcal{P}$ , it must generate an optimal transformed program  $\mathcal{P}^*$  according to the input data I. Each optimization module  $m_i \in \mathcal{M}$  has a unique input which is the program to be rewritten, and has an output  $\mathcal{P}' = m_i(\mathcal{P})$ . So, the final generated program  $\mathcal{P}^*$  is  $(m_n \circ m_{n-1} \circ \cdots \circ m_0)(\mathcal{P})$ .

We must have a clear concept and definition of a program transformation module. Nowadays, many optimization techniques are complex toolboxes with many parameters. For instance, loop unrolling and loop blocking require a parameter which is the degree of unrolling or blocking. Until Section 1.3, we do not consider such parameters in our formal problem. We handle them by considering, for each program transformation, a finite set of parameter values, which is the case in practice. Therefore loop unrolling with an unrolling degree of 4 and loop unrolling with a degree of 8 are considered as two different optimizations.

In order to check that the execution time has reached some value T, we assume that there is a computable performance evaluation function t that allows to precisely evaluate or predict the execution time (or other performance metrics) of a program  $\mathcal{P}$  according to the input data I. We assume the program  $\mathcal{P}$  always terminate. Let  $t(\mathcal{P}, I)$  be the predicted execution time. t can be either the measure of performance on the real machine, obtained through execution of the program with its inputs, a simulator or a performance model.

#### **Iterative Compilation**

The phase ordering problem corresponds to what occurs in a compiler: whatever the program and input be given by the user (if the compiler resorts to profiling), the compiler has to find a sequence of optimizations reaching some (not very well defined) performance threshold. Answering the question of the phase ordering problem as defined in Problem 1 depends on the performance prediction model t.

This problem corresponds to the case where t is not an approximates model but is the real executing machine (the most precise model). Let us present the intuition behind this statement: a compiler always has an architecture model of the target machine (resource constraints, instruction set, general architecture, latencies of caches,...). This model is assumed to be correct (meaning that the real machine conforms according to the model) but does not take into account all mechanisms of the hardware. Thus in theory, an infinite number of different machines fit into the model, and we must assume the real machine is any of them. As the architecture model is incomplete and performance also depends usually on non-modeled features (conflict misses, data alignment, operation bypasses,...), the performance evaluation model of the

$<sup>^{1}\</sup>circ$  denotes the symbol of function combination (concatenation).

compiler is incorrect. This suggests that the performance evaluation function of the real machine can be any performance evaluation function, even if there is a partial architectural description of this machine. Consequently, Problem 1 corresponds to the case of the phase ordering problem when t is the most precise performance model which is the real executing machine (or simulator): the real machine measures the performance of its own executing program (for instance, by using its internal clock or its hardware performance counters).

**Pb. 1** (Iterative Compilation Phase-Ordering) Let  $\mathcal{M}$  be a finite set of program transformations. For any performance evaluation function t,  $\forall T \in \mathbb{N}$  an execution time (in processor clock cycles),  $\forall \mathcal{P}$  a program,  $\forall I$  input data, the problem is to find a sequence  $s \in \mathcal{M}^*$  such that  $t(s(\mathcal{P}), I) < T$ ? In other words, if we define the set:

$$S_{\mathcal{M}}(t, \mathcal{P}, I, T) = \{ s \in \mathcal{M}^* | t(s(\mathcal{P}), I) < T \},$$

is the set  $S_{\mathcal{M}}(t, \mathcal{P}, I, T)$  empty?

Textually, this phase ordering problem tries to determine for each program and input whether there exists or not a compilation sequence s which results in an execution time lower than a bound T. It can be shown that if there is an algorithm that decides this problem then there is an algorithm that computes one sequence s such that  $t(s(\mathcal{P}), I) < T$ , provided that t always terminates.

We assume an additional hypothesis: there exists a program that can be optimized into an infinite number of different programs. This necessarily requires that there is an infinite number of different optimization sequences. But this is not sufficient. As sequences of optimizations in  $\mathcal{M}$  are considered as words made of letters from the alphabet  $\mathcal{M}$ , the set of sequences is always infinite, even with only one optimization in  $\mathcal{M}$ . For instance, fusion and loop distribution can be used repetitively to build sequences as long as desired. However, this infinite set of sequences will only generate a finite number of different optimized codes (ranging from all fusioned loops, to all distributed loops). If the total number of possible generated programs is bounded, then it may be possible to fully generate them in a bounded compilation time: it is therefore easy to check the performance of every generated program and to keep the best one. In our hypothesis, we assume that the set of all possible generated programs (generated using the distinct compilation sequences belonging to  $\mathcal{M}^*$ ) is infinite. One simple optimization such as strip-mine, applied many times to a loop with parametric bounds, generates as many different programs. Likewise, unrolling a loop with parametric bounds can be performed an infinite number of times. Note that the decidability of Problem 1 when the cardinality of  $\mathcal{M}^*$  is infinite while the set of distinct generated programs is finite remains an open problem.

**Theorem 1** Iterative Compilation Phase-Ordering is an undecidable problem if there exists a program that can be optimized into an infinite number of different programs.

## Library Optimization

We provide here a variation on the phase ordering problem that corresponds to the library optimization issue: program and (possibly) inputs are known at compile-time, but the optimizer has to adapt its sequence of optimization to the underlying architecture/compiler. This is what happens in Spiral [129] and FFTW [63]. If the input is also part of the unknowns, the problem has the same difficulty.

**Pb. 2 (Phase Ordering for Library Optimization)** Let  $\mathcal{M}$  be a finite set of program transformations,  $\mathcal{P}$  the program of a library function, I some input and T an execution time. For any performance evaluation function t, does there exist a sequence  $s \in \mathcal{M}^*$  such that  $t(s(\mathcal{P}), I) < T$ ? In other words, if we define the set:

$$S_{\mathcal{P},I,\mathcal{M},T}(t) = \{ s \in \mathcal{M}^* | t(s(\mathcal{P}),I) < T \}$$

is the set  $S_{\mathcal{P},I,\mathcal{M},T}(t)$  empty?

The decidability results of Problem 2 are stronger than those of Problem 1: here the compiler knows the program, its inputs, the optimizations to play with and the performance bound to reach. However, there is still no algorithm to find out the best optimization sequence, if the optimizations may generate a infinite number of different program versions.

**Theorem 2** Phase Ordering for library optimization is undecidable if optimizations can generate an infinite number of different programs for the library functions.

## **One-Pass Generative Compilers**

Generative compilation is a subclass of iterative compilation. In such simplified classes of compilers, the code of an intermediate program is optimized and generated in a one pass traversal of the abstract syntax tree. Each program part is treated and translated to a final code without any possible backtracking in the code optimization process. For instance, we can take the case of a program given as an abstract syntax tree. A set of compilation phases treats each program part, *i.e.* each sub-tree, and generates a native code for such part. Another code optimization module can no longer re-optimize the already generated program part, since any optimization module in generative compilation takes as input only program parts in intermediate form. When a native code generation for a program part is carried out, there is no way to re-optimize such program portion, and the process continues for other sub-trees until finishing the whole tree. Note that the optimization process for each sub-tree is applied by a finite set of program transformations. In other words, generative compilers look for local "optimized" code instead of a global optimized program.

Generative compilers making the assumption that sequences of best optimized codes are best optimized sequences fit the one-pass generative compiler description. For example, the SPIRAL project in [129] is a generative compiler. It performs a local optimization to each node. SPIRAL optimizes FFT formulae, from the formula level, by trying different decomposition of large FFTs. Instead of a program, SPIRAL starts from a formula, and the optimizations considered are decomposition rules. From a formula tree, SPIRAL recursively applies a set of program transformations at each node, starting from the leaves, generates C code, executes it and measures its performance. Using dynamic programming strategy<sup>2</sup>, composition of best performing formulae are considered as best performing compositions.

As can be seen, finding a compilation sequence in generative compilation that produces the fastest program is a decidable problem. Since the size of intermediate representation forms decreases at each local application of program transformation, we are sure that the process of program optimization terminates when all intermediate forms have been transformed to native codes. In other terms, the number of possible distinct passes on a program becomes finite and bounded: for each node of the abstract syntax tree, we apply locally a single code optimization (we iterate over all possible code optimization modules and we pick up the one that produces the best performance according to the chosen performance model). Furthermore, no code optimization sequence is searched locally (only a single pass is applied). Thus, if the total number of nodes in the abstract syntax tree is equal to  $\tilde{n}$ , then the total number of applied compilation sequences does not exceed  $|\mathcal{M}| \times \tilde{n}$ .

Of course, the decidability of one-pass generative compilers does not prevent them from having potentially high complexity: each local code optimization may be exponential (if it tackles NP-complete problem for instance). The decidability result only proves that, if we have a high computation power, we know that we can compute the optimal code after a bounded compilation time (possibly high).

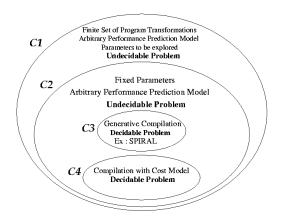

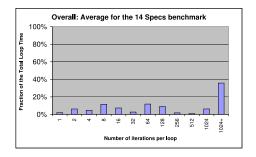

Figure 1.1 synthesizes a whole view of the different classes of the investigated problems with their decidability results. The largest class of the phase ordering problem that we consider, denoted by  $C_1$ , assumes a finite set of program transformations with possible optimization parameters (to explore). If the performance prediction function is arbitrary, typically if it requires program execution or simulation, then this problem is undecidable. The second class of the phase ordering problem, denoted by  $C_2 \subset C_1$ , has the same hypothesis as  $C_1$  except that the optimization parameters are fixed. The problem is undecidable too. However, we have identified two decidable classes of phase ordering problem which are  $C_3$  and  $C_4$  explained as follows. The class  $C_3 \subset C_2$  considers one-pass generative compilation; the program is taken as an abstract syntax tree (AST), and code optimization applies a unique local code optimization module on each node of the AST. The class  $C_4 \subset C_2$  takes the same assumption as  $C_2$  plus an additional constraint which is the presence of a cost model: if the cost model is a discrete increasing function, and if the cost of the code optimization is bounded, then  $C_4$  is a class of decidable phase ordering problem.

<sup>&</sup>lt;sup>2</sup>The latest version of SPIRAL use more elaborate strategies, but still does no resort to exhaustive search/test.

Figure 1.1: Classes of Phase-Ordering Problems

The next section investigates another essential question in optimizing compilation, which is parameters space exploration.

## 1.3 Towards a Model for Best Optimization Parameters

Nowadays, many compiler optimization methods are parameterized. For instance, loop unrolling requires an unrolling degree; loop blocking requires a blocking degree as well, etc. Actually, the complexity of phase ordering problem does not allow to explore jointly the the best sequence of the compilation steps and the best combinations of modules parameters. Usually, the community tries to find the "best" parameter combination when the compilation sequence is fixed. This section is devoted to study the decidability of such problem.

First, we suppose that we have  $s \in \mathcal{M}^*$  a given sequence of optimizing modules belonging to a finite set  $\mathcal{M}$ . We assume that s is composed of n compilation sequences.

We associate for each optimization module  $m_i \in \mathcal{M}$  a unique integer parameter  $k_i \in \mathbb{N}$ . The set of all parameters is grouped inside a vector  $\overrightarrow{k} \in \mathbb{N}^n$ , such that the  $i^{th}$  component of  $\overrightarrow{k}$  is the parameter  $k_i$  of the  $m_i$ , the  $i^{th}$  module inside the considered sequence s. If the sequence s contains multiple instances of the same optimization module m, the parameter of each instance may have a distinct value from those of the other instances.

For a given program  $\mathcal{P}$ , applying a program transformation module  $m \in \mathcal{M}$  requires a parameter value. Then, we write the transformed program as  $\mathcal{P}' = m(\mathcal{P}, \overrightarrow{k})$ .

As in the previous sections devoted to the phase ordering problem, we assume here the existence of a performance evaluation function t that predicts (or evaluates) the execution time of a program  $\mathcal{P}$  having I as input data. We denote  $t(\mathcal{P}, I)$  the predicted execution time. The formal problem of computing the best parameter values of a given set of program transformations in order to achieve the best performance can be written as follows.

#### Polynomial Performance Model

In this chapter, we assume that the performance prediction function is built by an algorithm **a**, taking s and  $\mathcal{P}$  as parameters. Moreover, we assume the performance function  $t = \mathbf{a}(\mathcal{P}, s)$  built by **a** takes  $\overrightarrow{k}$  and

I as parameters and is a polynomial function. Therefore, the performance of a program  $\mathcal{P}$  with input I and optimization parameters  $\overrightarrow{k}$  is  $\mathtt{a}(\mathcal{P},s)(I,\overrightarrow{k})$ . We discuss about the choice of a polynomial model after the statement of the problem. We want to decide whether there are some parameters for the optimization modules that make the desired performance bound reachable:

**Pb. 3 (Best-Parameters)** Let  $\mathcal{M}$  be a finite set of program transformations and s a particular optimization sequence of  $\mathcal{M}^*$ . Let a be an algorithm that builds a polynomial performance prediction function, according to a program and an optimization sequence. For all programs  $\mathcal{P}$ , for all inputs I and performance bound T, we define the set of parameters as:

$$P_{s,t}(\mathcal{P}, I, T) = \{\overrightarrow{k} | \mathbf{a}(\mathcal{P}, s)(\overrightarrow{k}, I) < T\}.$$

Is

$$P_{s,t}(\mathcal{P}, I, T)$$

empty ?

As noted earlier, choosing an appropriate performance model is a central decision to define whether Problem 3 is decidable or not. Problem 3 considers polynomial functions, which are a family of usual performance models (arbitrary linear regression models for instance). Even a simple static model of complexity counting assignments evaluates usual algorithms with polynomials ( $n^3$  for a straightforward implementation of square matrix-matrix multiply for instance). With such a simple model, any polynomial can be generated. It is assumed that a realistic performance evaluation function would be as least as difficult as a polynomial function. Unfortunately, the following theorem shows that if t is an arbitrary polynomial function, then Problem 3 is undecidable.

The following theorem states that Problem 3 is undecidable if there are at least 9 integer optimization parameters. In our context, this requires 9 optimizations in the optimizing sequence. Note that this number is constant when considering the best parameters, and is not a parameter itself. This number is fairly low compared to the number of optimizations found in state-of-the-art compilers (such as gcc or icc for instance). Now, if t is a polynomial and there are less than 9 parameters (the user has switched off most optimizations for instance): if there is only one parameter left, then the problem is decidable. For a number of parameters between 2 and 8, the problem is still open [107] and Matiyasevich conjectured it as undecidable.

**Theorem 3** The Best-Parameters Problem is undecidable if the performance prediction function  $t = a(\mathcal{P}, s)$  is an arbitrary polynomial and if there are at least 9 integer optimization parameters.

#### Finite Parameter Space

Our formal problem Best-Parameters is the formal writing of library optimizations. Indeed, in such area of program optimizations, the applications are given with a training data set. Then, people try to find the best parameter values of optimizing modules (inside a compiler usually with a given compilation sequence) that holds in the best performance. In this section, we show that some simplified instances of Best-Parameters problem becomes easily decidable. A first example is the OCEANS project [1], and a second one is the ATLAS framework [157].

The OCEANS project [1] optimizes a given program for a given data set by exploring all combinations of parameter values. Potentially, such value space is infinite. However, OCEANS restricts the exploration to finite set of parameter intervals. Consequently, the number of parameter combinations becomes finite, allowing a trivial exhaustive search of the best parameter values: each optimized program resulting from a particular value of the optimization parameters is generated and evaluated. The one performing best is chosen. Of course, if we use such exhaustive search, the optimizing compilation time become very high. So, one can provide efficient heuristics for exploring the bounded space of the parameters [150].

ATLAS [157] is another simplified case of the Best-Parameter problem. In the case of ATLAS, the optimization sequence is known, the programs to optimize are known (BLAS variants), and it is assumed that the performance does not depend on the value of the input (independence w.r.t. the matrix and vector values). Moreover, there is a performance model for the cache hierarchy (basically, the size of the cache) that, combined to the dynamic performance evaluation, limits the number of program executions

(i.e., performance evaluation) to do. For one level of cache and for matrix-matrix multiplication, there are three levels of blocking controlled by three parameters, bounded by the cache size and a small number of loop interchanges possible (for locality). Exhaustive enumeration inside admissible values enable to find the best parameter value.

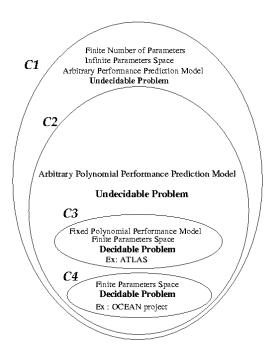

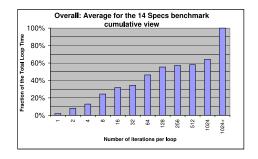

Figure 1.2: Classes of Best-Parameters Problems

Figure 1.2 synthesizes a whole view of the different classes of the investigated problems with their decidability results. The largest class of the best parameters exploration problem that we consider, denoted by  $C_1$ , assumes a finite set of optimization parameters with unbounded values (infinite space); The compiler optimization sequence is assumed fixed. If the performance prediction function is arbitrary, then this problem is undecidable. The second class of the best parameters exploration problem, denoted by  $C_2 \subset C_1$ , has the same hypothesis as  $C_1$  except that the performance model is assumed as an arbitrary polynomial function. The problem is undecidable too. However, a trivial identified decidable class is the case of bounded (finite) parameters space. This is the case of the tools ATLAS (class  $C_3$ ) and OCEANS (class  $C_4$ ).

## 1.4 Outline of the Document

The first two chapters are dedicated to optimization with and through high performance libraries. Chapter 2 presents automatic methods to detect then rewrite fragments of an application with calls to predefined high performance library functions and templates. Chapter 3 describes methods and performance model for a hierarchical approach to code optimization, defining libraries of kernels tuned for the optimization of a code. First applied to linear algebra library codes, the techniques are applied and adapted to more general applications.

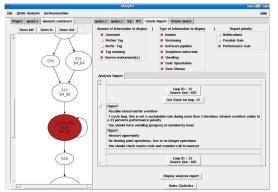

Finally, Chapter 4 focuses on assembly code performance analysis and optimization. Based on a combination of static and dynamic analyses (instantiated in a tool, MAQAO), two approaches for optimization

are proposed, one of them building a set of binary templates instantiated and reused at run-time. Chapter 5 sums up the contributions of this work and proposes some perspectives.

# Chapter 2

# Refactoring with Performance Libraries

The subject of this chapter is to propose another way to improve application performance, by detecting automatically code fragments that can be replaced by high performance library function calls. All the work presented here, initiated in collaboration with Paul Feautrier and Xavier Redon [17] is fully described in Christophe Alias PhD thesis [4].

## 2.1 Introduction

The traditional approach in program optimization consists in applying successive transformations to the code in order to reach a high level of performance. Due to the large number of hardware mechanisms to trigger, the optimizations are complex and numerous, interactions between different optimizations are not fully comprehended and performance of the generated code is highly sensitive to the input data. As a consequence, there is a chance that compiler optimizations degrade performance, implying that performance tuning requires expert knowledge in architecture, optimizing techniques and application context, and a large amount of time in any case.

In order to reuse the effort and time spent to optimize similar code fragments, two alternatives are generally considered as a more reliable way to deliver performance for performance critical codes:

- High performance libraries: The assembly code of library functions is usually generated by hand, using architecture specific instructions, or by adaptative compilation (e.g. ATLAS [156], Spiral [129], FFTW [64]). The important compilation time is then balanced by the reusability of the libraries. In all cases, library functions can be considered as the building blocks, essential to get high performance on real codes. In general programming languages, code tuning is performed in the last stage of the development process. The selection of the library functions and the rewriting of the code falls under the responsibility of the user. The usual steps of this process are: find out code fragments and library functions that are semantically equivalent, replace these fragments by function calls with correct parameters, debug the application and finally evaluate performance. In the case of non-portable libraries, this time consuming process has to be reconducted for each target architecture. This is surprising how little the compiler helps the user in this tedious task. Compile-time optimizations neither change the partition between library and user code, nor cross library boundaries. This stresses furthermore the importance of this manual partitioning for performance.

- Domain specific languages: With domain-specific languages, algorithms are described in a more abstract and compact way than with traditional imperative programming languages. Expressing algorithms at a higher level of abstraction adds portability and improves programmer productivity for code writing and maintenance. All domain specific languages are not performance oriented, however

the higher the representation of the program, the more aggressive the compiler optimizations can be: for instance a generative approach can yield from a mathematical formula in SPIRAL [129] a finely tuned code for a particular architecture, exploring both algorithmic variations and traditional code optimizations, finding a large degree of parallelism. The same benefit appears also for code verification. However, this approach assumes that the user specifies his algorithm using a domain-specific language. Starting from an existing C or Fortran program and finding in it fragments that correspond to domain specific templates would be desirable but seems difficult to obtain.

Of course, the generation of these high performance building blocks (either libraries or basic operations for the DSL) is still an issue and it will be discussed in next chapters. Assuming there are high performance libraries available (or a DSL with its types and operations), developers starting from a code, written in C for instance, still have to decide manually where and when to call performance libraries. This transformation is called here code refactoring with libraries, as refactoring [60] stands for

"...restructuring an existing body of code, altering its internal structure without changing its external behavior."

This chapter explores methods that automatically find in a program the code fragments that correspond to known library functions. This enables a refactoring of the code, using high performance library function codes. To some extent, it is possible in some cases to rewrite a C code into a DSL program, based on the decomposition into library functions. Recognizing functions in a code and rewriting the code with these function calls in order to improve performance is a difficult task. As a matter of fact, this approach is not easier than applying transformations on a code in order to obtain high performance. Indeed it boils down to algorithm recognition, an old problem in computer science: Basically, one would like a compiler to automatically find that lines 10 to 23 are an implementation of a DFT for instance. A natural solution would be to search the code for patterns of known functions (matrix-matrix product, tensor product or direct sum for the DFT). Such a facility would enable many important techniques, that are out of reach for traditional optimization techniques:

- Program comprehension and reverse engineering: we can rewrite part of the code with a higher level language, enhancing code maintenance and portability.

- Program optimization: if we have the necessary items in our library or if we can use a generative approach, we may replace lines 10 to 23 by an automatically tuned version. We may even replace the relevant part of the code by a completely different implementation.

- Program verification: if we know that the program specification asks for a DFT and the analyzer does not find it, we may suspect an error.

- Hardware-software co-design: if we recognize in the source program a piece of code for which we have a hardware implementation (e.g. as a co-processor or an Intellectual Property component) we can remove the code and replace it by an activation of the hardware.

The approach described in this chapter relies on the results of a program dependence analysis and is three-fold: (i) Find efficiently all code fragments of the applications that "may" be similar to some known functions implemented in high performance libraries. These code fragments are called *slices*. The linear complexity of this step is important since it analyzes all the application code and dependence analysis is a simple SSA. (ii) Compare the selected slices with library functions and keep only those that "must" be equivalent. Here, the dependence analysis required is an instance-wise reaching definition analysis (iii) Replace the code fragments selected by the appropriate function call in the program, or build a higher representation of the code in some DSL (we will consider this problem with SPIRAL).

The following sections follow this sequence. In the rest of the introduction, we propose a motivating example, showing all the steps required for the algorithm detection. We then provide some definitions for the equivalence, and introduce some required technical notions. Section 2.3 presents the fast detection of a potential pattern in the code, Section 2.4 describes the instantiation test and finally, we describe in Section 2.5 the conditions for which code substitution by function calls is possible and beneficial.

## 2.2 Program Equivalence

We focus on imperative programs written in C or Fortran. The libraries considered are template libraries (with the meaning of C++ templates). A template function, also called *pattern*, is a function depending on input variables and on some input functions (usually these functions are associated to the class of the variables given as input). Note that as a prerequisite for the detection step, each library function has to be described by a program. We do not assume that the analysis has access to the source of the library. Instead we assume the library designer provides a public version for each function. This program must have the same semantic as the optimized, private version but the algorithm used can be completely different. Moreover, we assume the library templates are static control programs [59].

Finding instances of a pattern in a program means finding all program slices equivalent to an instance of the pattern. But what does exactly mean "equivalent"? We will consider a weak version of semantic equivalence called *Herbrand-equivalence*. Instead of deciding whether two algorithms compute the same (mathematical) function, Herbrand-equivalence just states that they compute the same mathematical formula, syntactically (no associativity, no commutativity involved for instance). It means that if we consider the values computed by a code as terms depending on the inputs, an equivalent program computes exactly the same terms. In this way, Herbrand-equivalence can be considered as a true algorithmic equivalence. Even if Herbrand-equivalence is weaker than semantic equivalence, and seems to be easier to check, we have unfortunately proved that it is undecidable, even for the simple comparison of two programs (no template):

**Theorem 4** The problem of Herbrand-equivalence between two static control programs is undecidable.

The proof is given in [17] and boils down to the tenth Hilbert Problem. It entails that the problem of matching, that is, finding all instances of a template in a code is also undecidable. Within this framework, the method presented is conservative: some of the fragments found are not semantically equivalent to the library codes, but none of the truly equivalent fragments is missed.

Obviously the equivalence is interesting only if a slice can be considered as an instantiation of the template even when they are not syntactically equal (otherwise simple pattern matching technique is sufficient). Herbrand equivalence can abstract away some variations between the slice and the template function. Program variations can arise from data structure variations (coming from scalar promotion, array expansion, structures instead of arrays,...), control variations (coming from loop fusion, unroll, skewing,...), organization variations (coming for permutation of program statements) or semantic variations (using associativity or commutativity for instance). Only semantic variations are not handled by the techniques proposed in this chapter.

The equivalence problem can be seen as a way to find sequences of transformations (control and data layout) where the objective is no longer to increase performance, but to involve a given high performance template.

# 2.3 Finding Slices similar to Template

The detection of library templates consists in localizing in a code the lines that possibly correspond to a given library function or template. In the case of a template, the code detected is a possible instance of the template. We propose an efficient method based on a symbolic execution of both program and template, following the def-use chains. The method symbolically executes both program and template slices simultaneously and compares the sequence of operators along these slices, abstracting away the number of iterations of the loops.

We assume that programs and templates are given in SSA form, a classical form in compilation that provides def-use chains. For the sake of clarity, we assume that each statement has one operator at most. Each edge of the program SSA-graph is labeled with its operator. Loops create cycles in this graph but we abstract away the number of iterations. The sequence of operators along a path is considered as a word and the graph can be considered as a finite automaton. The idea of the algorithm is to check whether the language of operators generated by some code fragment is included in the language of operators generated

by a library function. Intuitively, this ensures that the same sequence of operations can happen in the code and in the library function.

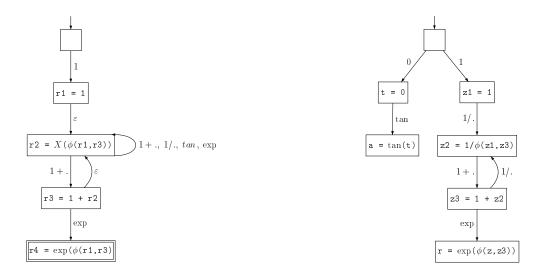

Consider the toy example given in figure 2.1. Statements assigning a constant such as  $T_1$ ,  $P_1$  or  $P_2$  have no predecessors in the graph of def-use chains, they can be taken as a starting point for the inspection. Following the def-use chains, starting from  $P_1$ , the sequence  $\xrightarrow{1} P_1 \xrightarrow{1/...} P_4 \xrightarrow{1+...} P_5 \xrightarrow{\exp} P_6$  is

$$T_1$$

r1 = 1  $P_1$  z1 = 1  $P_2$  t = 1  $P_2$  t = 1  $P_3$  a = tan(t)  $P_3$  a = tan(t)  $P_4$  cenddo  $P_4$  cenddo  $P_4$  cenddo  $P_4$  cenddo  $P_5$  cenddo  $P_6$  r = exp( $\phi$ (r1,r3)) (a) Template (b) Code

Figure 2.1: Example of Template and Program. The template corresponds to a slice of the program.

obtained. Likewise for the template a possible sequence of operators is:

$$\xrightarrow{\quad 1\quad }T_{1}\xrightarrow{\quad X(.)\quad }T_{2}\xrightarrow{\quad 1+.\quad }T_{3}\xrightarrow{\quad \exp\quad }T_{STOP}.$$

Walking through both program and template, with the condition that for each transition, the operator must be the same, we obtain the sequence:

$$\xrightarrow{1} (T_1, P_1) \xrightarrow{1/..X(.)=1/.} (T_2, P_4) \xrightarrow{1+..} (T_3, P_5) \xrightarrow{\exp} (T_{STOP}, P_6).$$

This provides the candidate slice  $\{P_1, P_4, P_5, P_6\}$ , that possibly corresponds to the template provided that X(.) = 1/. (this condition appears on the transition). This condition is necessary for the sequence to be the same for both template and program. Note however that the method will not check the coherence between the values of template variables if they appear multiple times. Likewise, the number of iterations in loops or the branches chosen in conditionals are ignored. These important points will be checked during the exact instantiation test (see Section 2.4).

Because most operators have an arity greater than 2, word automata are not expressive enough in general. Our detection algorithm, detailed in [7, 8] uses a powerful extension of automata called tree-automata. A tree automaton is a tuple  $\mathcal{A} = (\Sigma, Q, Q_f, \Delta)$ , where  $\Sigma$  is a signature, Q the set of states,  $Q_f \subset Q$  the set of final states, and  $\Delta$  a set of transition rules of the type  $f(q_1 \dots q_n) \longrightarrow q$ , where  $n \geq 0$ ,  $f \in \Sigma$  and  $q, q_1, \dots, q_n \in Q$ . Tree automata were introduced by Doner [51, 52] and Thatcher and Wright [142] in the context of circuit verification. Most of usual operations on word automata (determinization, minimization, Cartesian product, ...) extend naturally to tree automata [36]. There is no major difference with the word automata: we associate a state to each assignment then we add transitions according to the dependences given by the  $\phi$ -functions. X, as a wild-card can be unified to any other operator.

Consider the pattern and the program given in figure 2.1. For sake the of clarity, we have chosen a pattern and a program with unary operators which will lead to the word automata given in figure 2.2. But of course, our method can handle operators with any arity. The  $\phi$ -functions can be seen as multiplexers selecting the last definition for a given value.

The idea is now to step simultaneously the two automata down to the pattern final state (in the Figure, beginning with r4=...) while the operators are equal. The two automata have as many entry points as constant leaves (0 and 1 here), and we have to start a comparison from each couple of leaves. The operations corresponds to the definition of the *Cartesian product* of the pattern and program automata. The detected slices can then be computed by collecting all program states along the paths from initial states to each state with a final pattern state.

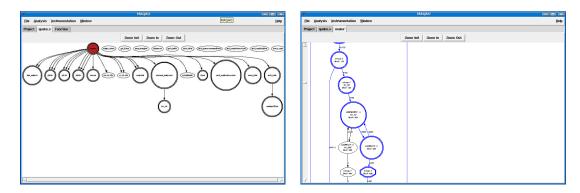

Figure 2.2: Example of Pattern automaton (left), and Program automaton (right)

This method is able to detect any template variation which does not involve the semantic properties of operators such as associativity, or commutativity. Particularly it handles any loop transformation and most control restructuring transformations. Moreover, our method is completely independent of data structure used, which allows the detection of a large amount of template variations in the program. Whether a slice detected is a real instantiation of the template is determined during the exact instantiation test (next section). In the worst case, the construction of the Cartesian product of the template and the program automata is computed in  $O(T \times P)$  where T is the number of template statements and P is the number of program statements, i.e. the complexity is linear in the size of the program analyzed.

# 2.4 Exact Template Instantiation

The exact instantiation test consists in deciding whether a particular code is an instantiation of a given template. Templates considered are static control programs, and the code compared to is one of the slices extracted described in previous section. A template is considered as a program with some re-definable functions and inputs, as templates in C++ operating on parametric types.

For a program  $P, P \downarrow$  denotes the term obtained by completely unfolding the computation of P. This term is well-defined for a program P with a schedule (no infinite loop). Likewise, for a template T with a schedule, the term  $T \downarrow$  exists. These terms correspond to the symbolic term computed by the codes depending on the inputs. The matching problem is to find a substitution  $\sigma$  of the template variables such that  $\sigma(T \downarrow)$  is syntactically equal to  $P \downarrow$ . Such a substitution, if it exists, is called a *unifier* of the matching problem between T and P. This problem depends clearly on the underlying algebra. It is clear, however, that equivalence in the Herbrand universe implies equivalence in all conforming algebras. We only consider in this chapter equivalence in the initial algebra (no semantics). In particular  $\phi$ -functions are not given any interpretation during the resolution of the matching problem.

In order to give the intuition of the method, we study the case of the template and code in Figure 2.3 when n = 2. We can completely unfold the recurrence of the template, the output is:

$$X(X(Y[0], Y[1]) * 2, Y[2]) * 2$$

For the program in SSA form (Figure 2.3(c)), the output is:

$$\phi_{OUT}(0, \phi_{S_3}(\phi_{S_1}(0, S_3[1] * 2), \phi_{S_1}(0, S_3[1] * 2) + 1) * 2)$$

```

MAX = I[0]

MO = I[0]

a = Y[0]

do i = 1, n

S = 0

SO = 0

a = X(a,Y[i])*2

do i = 1, n

do i = 1, n

enddo

if (MAX < I[i]) then

S1 = \phi(S0,S4)

OUT = a

MAX = I[i]

M1 = \phi(M0,M3)

S = S+1

if (M1 < I[i]) then

endif

M2 = I[i]

S = S*2

S2 = S1+1

enddo

endif

OUT = s

S3 = \phi(S1,S2)

M3 = \phi(M1, M2)

S4 = S3*2

enddo

OUT = \phi(S0,S4)

(a) Template

(b) Slice to analyze

(c) SSA form of the slice

```

Figure 2.3: Example of template and slice to compare. X and Y are input function and array of the template.

with

$$S_3[1] = \phi_{S_3} (\phi_{S_1} (0, S_4[0]), \phi_{S_1} (0, S_4[0]) + 1)$$

Note that in the preceding expressions,  $S_4[0]$  is not defined, its value will be denoted  $\perp$ .

The problem is to find out the possible values of X and Y such that the two expressions are the same, syntactically. Hence, the problem of matching is reduced to a semi-unification problem, between the terms of the template and of the program, where unknowns are template variables (here X and Y), and closed variables are program inputs (here I[0], I[1] and I[2]).

To unify two terms, we can apply Huet procedure [77]. Basically, we try to decompose the problem by applying the rule:  $f(\vec{t}) \stackrel{?}{=} f(\vec{t'}) \rightarrow t_1 \stackrel{?}{=} t'_1 \wedge \ldots \wedge t_n \stackrel{?}{=} t'_n$  until terms of the form  $X(\vec{t}) \stackrel{?}{=} f(\vec{t'})$  are obtained, where X is a template variable. Then we try to construct an unifier by trying:

- Projections:  $X(\ldots x_k \ldots) = x_k$ ;

- Imitation:  $X(\vec{x}) = f(X_1 \vec{x} \dots X_n \vec{x})$ , with the  $X_i$  new function variables.

When a decomposition is not possible because the two head operators are different, then this is a failure, the program and template are not equivalent. When one of these operators is a  $\phi$ -function then this function has to be computed in order to avoid the failure of the method. The value of a  $\phi$ -function can only be one of its arguments. A dependence analysis may be enough to find out the argument defining the function. Otherwise, more complex data-flow analyses are necessary [59, 127, 108]. It may happen that a  $\phi$ -function cannot be evaluated when the code containing it is outside the scope of the data-flow analysis. In this case, the  $\phi$ -function remains uninterpreted and the unification fails, the template is then said non-equivalent to the program. This is a safe approximation.

On the example, we try to decompose the head operator in both expressions: for the code, this is  $\phi_{OUT}$ , for the template this is \*. Thus  $\phi_{OUT}$  must be computed: as we have supposed that  $n \geq 0$ , a dependence analysis can show that  $\phi_{OUT}(x,y) = y$ . This is equivalent to prove that at least one iteration of the loop is executed. The head operator is \* now in both terms. By decomposition, we have to match  $X(X(\ldots), Y[2]) \stackrel{?}{=} \phi_{S_3}(\phi_{S_1}(\ldots), \phi_{S_1}(\ldots))$ . By applying the rule imitate, we define X(x,y) as  $\phi_{S_3}(X_1(x,y), X_2(x,y))$  where  $X_1$  and  $X_2$  are new template variables and the next step is a decomposition for  $\phi_{S_3}$ . Note that here, there is no need to compute the exact value of  $\phi_{S_3}$ . Finally, by an exhaustive application of the procedure, the solution  $X(x,y) = \phi_{S_3}(\phi_{S_1}(0,x),\phi_{S_1}(0,x)+1)$  and  $Y[0] = \bot$  is found. The semantics of the  $\phi$ -functions is:

$$\phi_{S_1}(x,y) = \text{ if } i > 1 \text{ then } y \text{ else } x, \phi_{S_3}(x,y) = \text{ if } M_1[i] < I[i] \text{ then } y \text{ else } x.$$

Therefore, the function X of the template of Figure 1.b is, in a more natural way:

$$X(x,y) = \begin{vmatrix} \mathbf{if} \ M_1[i] < I[i] \\ \mathbf{then} \ \begin{pmatrix} | \ \mathbf{if} \ i > 1 \\ \mathbf{then} \ x \\ \mathbf{else} \ 0 \end{vmatrix} + 1$$

$$\mathbf{else} \begin{vmatrix} \mathbf{if} \ i > 1 \\ \mathbf{then} \ x \\ \mathbf{else} \ 0 \end{vmatrix}$$

Computation of  $M_1$ , used by X, can be added likewise to the definition of X.

In order to generalize this intuition for programs and templates with parametric loop bounds, the terms considered have a parametric length. Huet rewriting procedure is then no longer applicable as it is. The key idea is to build a finite automaton that compares the expressions computed by the program and the template and then to check if the states corresponding to failures in the unification procedure are reachable. The automaton proposed in [6] belongs to memory state automata[21] (MSA). Final states in the automaton express either failure of the unification, or success. In the later case, the unifier can be found by computing the reachability relation of the final state. All relations on the edges of the automaton are in Presburger arithmetics (thanks to the fact that the template is a static control program), and computing reachability relation boils down to computing a transitive closure of affine relations. This is what limits the method to a semi-algorithm, since the computation of transitive closures is undecidable. The construction of an MSA in order to check if the template matches the program was first proposed in [17], limited to templates without variable functions, generalized to templates in [6] and extended to templates containing loops in [4] with tree automata.

# 2.5 Rewriting Code with Library Calls

Given a template, applying the slice detection method on a program, followed by the instantiation tests defines the set of every code fragments matching the template, with the corresponding instantiation of the template functions. Now, it remains to transform these code fragments into library calls with their appropriate parameters (the inputs of the functions). Several difficulties arise for this code transformation, particularly if we want to improve performance:

- Legality [7]: replacing a code fragment by a semantically equivalent call to a library function does not always preserve the application semantics. Indeed, the library functions are assumed to be pure (no side effect, inputs are not modified), thus any variable modified in the code fragment should not be used outside of it, with the exception of the value returned by the library function .When this condition is not met, the transformation can be legal only by duplicating some amount of computation. This possibility has not been studied here, due to the potential performance loss induced.

- Trivial template instantiations: a dot product can be considered as a particular matrix-vector multiplication. It entails that all dot products will be also detected as matrix-vector multiplications. Worse, all scalar multiplications can be seen as dot products of size 1 vectors. These special instantiations of templates, getting rid of one dimension, should not be considered for refactoring.

- Overlapping instantiations: when considering different templates, the same code fragment can be part of two or more template instantiations. Moreover, a matrix-vector multiplication is usually written as several dot products. Choosing to replace all dot products by their library counterpart may prevent the more profitable transformation of matrix-vector operations with library functions. A cost model, discussed in the following, is required in this case.

- Data-layout Transformations Overhead: one of the strength of the method is to cope with some data layout transformations. In particular, array copies are no-ops for the recognition procedure. These

copies may be necessary in order to match the arrays of the program with the inputs of the library function. They have a cost that must be taken into account in order to decide whether it is worth or not to use the library function. Similarly to the previous item, a cost model is required.

• Aggregation of instantiations [8]: different consecutive code fragments may match the same template. Aggregating these fragments may make a bigger template instantiation (of the same pattern or of another one). A possible solution, discussed in the following, would be to create a hierarchy of templates, making possible the detection bottom-up of some templates from the detection of simpler ones.

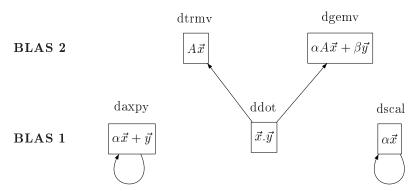

The detection techniques we proposed are able to detect the occurrences of template with only one output statement. Figure 2.4 provides an example of matching, where the template is the daxpy function of BLAS 1. Our slicing method yields the candidates slices  $S_1$  and  $S_2$ , but the candidate  $S_1 \cup S_2$  where a=2,  $\vec{x}=[s(1),s(2),s(3),u]$  and  $\vec{y}=[1,1,1,v]$  is missing since its outputs are shared by several statements. The same problem arises from (partially) unrolled parallel code, there are as many instantiations as the unrolling factor. Here, the solution would be to vectorize s(i) with u in order to build a bigger vector for daxpy. In

Figure 2.4: Two detections of daxpy

general, aggregation induces a hierarchy between algorithms, and particularly between templates. Typically, a daxpy is an aggregation of several scalar daxpy, and a matrix-vector product is an aggregation of dot products. Figure 2.5 provides an aggregation hierarchy between some BLAS 1 and 2 functions.  $A \to B$  means "B is an aggregation of A instances". We proposed in [8] a simple method to perform aggregation

Figure 2.5: Aggregation hierarchy of BLAS 1 and 2 functions

based on a predefined hierarchy of templates.

In order to handle the overlapping of two or more detected functions, a benefit is associated to each substitution so that the combination of substitutions bringing the maximum benefit can be found by integer linear programming. The problem is similar to code instruction selection ([57, 54] to name a few), extended to expressions of parametric length with patterns including loops. A simple approach is to assume that the benefit corresponds to the gain (in cycles for instance) brought by the library function. As this gain depends on the number of loop iterations performed by the function, an approximation is to evaluate this gain based on the total number of iterations when the iteration domains are polyhedra [32]. In any case, the benefit of a substitution is expressed as a polynomial expression. A first approximation would be to select, by integer linear programming, the solution maximizing the benefit for asymptotically large iteration count, taking into account that templates overlapping are mutually exclusive.

Finally, our detection method handles variations due to data layout. It means that a dot product is detected on the following loop (from LINPACK):

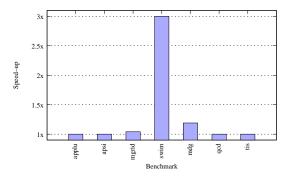

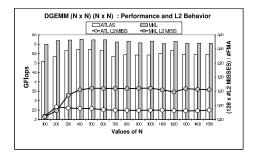

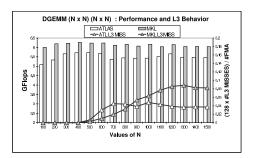

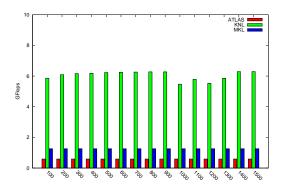

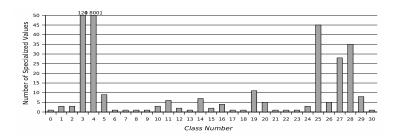

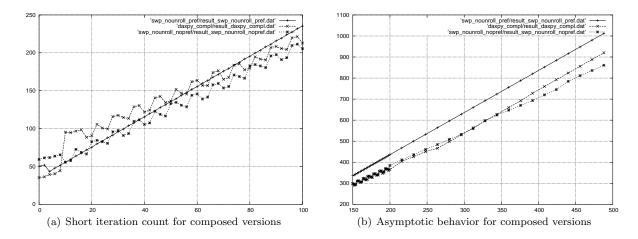

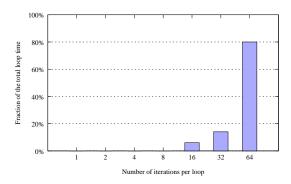

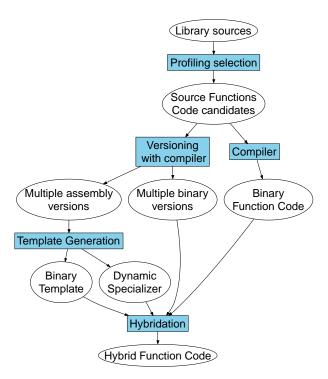

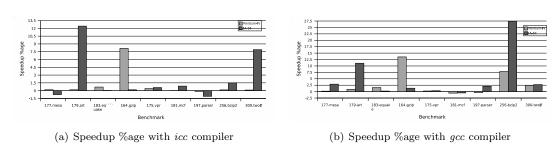

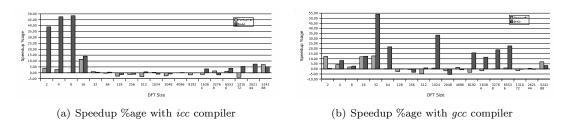

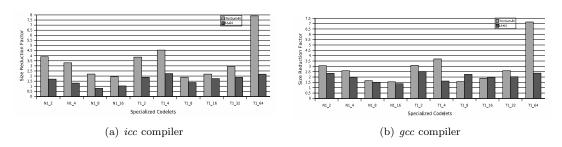

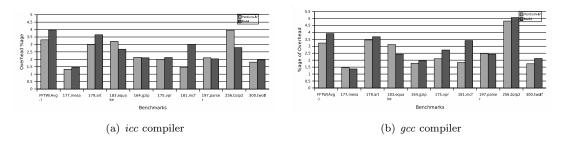

Rewriting this loop as a function call to a BLAS1 dotprod would require to copy elements of a and dx into the same array. The performance overhead added would be larger than any performance gain expected from the BLAS1 function. Finding an adequate performance model taking into account this kind of additional code (copy-in and out of intermediate data structures) is one of the major issues that need to be tackled in order to ensure that code refactoring with library functions improves performance.