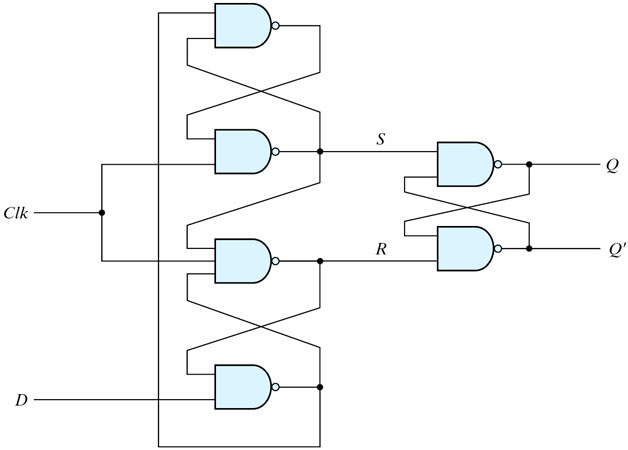

TD Circuits Séquentiels : Bistable D

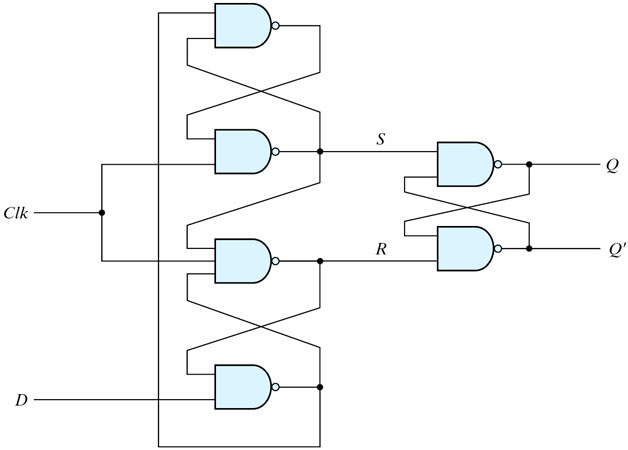

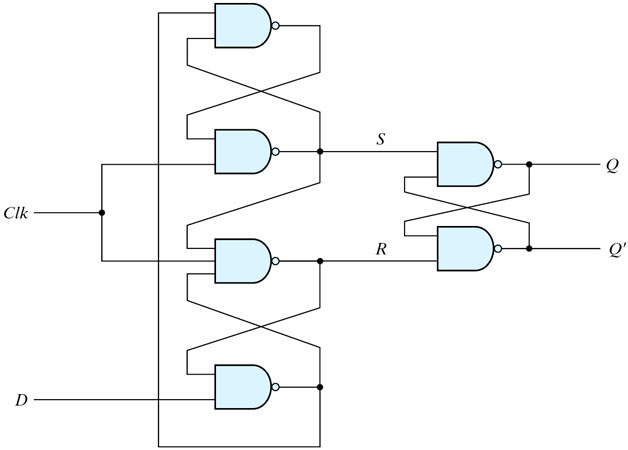

Voici une réalisation possible d'un bistable D

(flip-flop)

avec trois bascules SR,

de telle sorte que le signal d'entrée D

soit copié sur le signal de sortie Q

lorsque le signal d'horloge (Clk) passe de 0 à 1

(front montant) ;

dans tous les autres cas

(le signal d'horloge est stable à 0 ou 1,

ou bien passe de 1 à 0), le signal Q est inchangé,

même si le signal D est modifié.

(a)

- Montrer que la bascule SR,

qui est réalisée avec des portes NAND,

vérifie les équations suivantes :

- S = 0 et R = 1 impliquent

Q = 1 et Q' = 0.

- S = 1 et R = 0 impliquent

Q = 0 et Q' = 1.

- S = 1 et R = 1 impliquent

que Q et Q' gardent leurs valeurs.

- On suppose que le signal d'horloge Clk

vaut 0. Montrer que

S = R = 1 ;

compléter sur le diagramme (a) les valeurs des signaux

(autres que Q et

Q' )

en fonction de D

— on notera D' la négation de D.

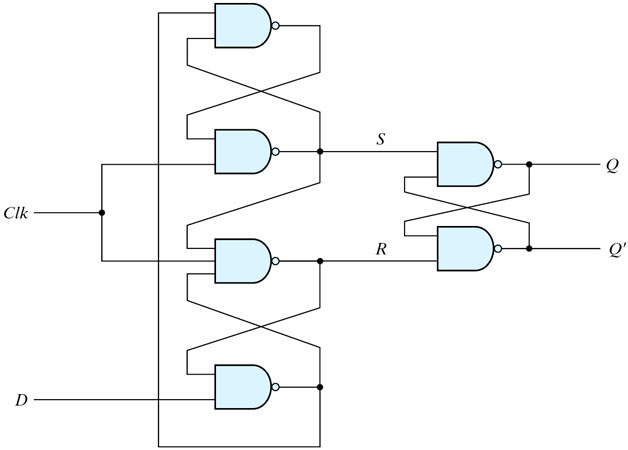

- On suppose que le signal d'horloge Clk

passe de 0 à 1. Etudier la propagation de ce changement

de signal à travers les différentes portes

et écrire les valeurs sur le diagramme (b) ;

quelles sont les valeurs de S et R

en fonction de D ?

En déduire qu'on a bien

Q = D .

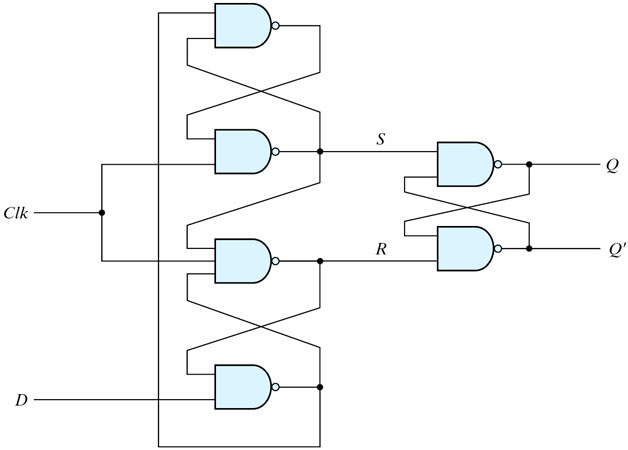

- On suppose que

pendant que le signal d'horloge Clk

vaut 1, la valeur du signal D change ;

étudier la propagation de ce changement

de signal à travers les différentes portes

et écrire les valeurs sur le diagramme (c) ;

montrer que les signaux S et R

ne sont pas modifiés.

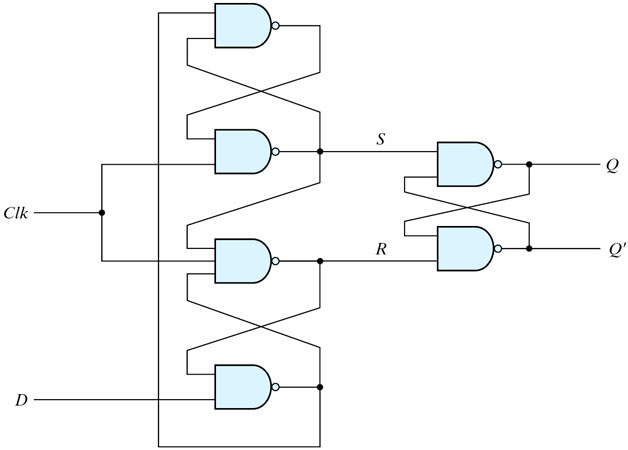

- Reste-t-il des cas à traiter ?

Peut-on avoir

S = R = 0 ?

Copie (b)

Copie (c)

Corrigé

Versions ppt

et pdf

(la première est plus animée).